#### **CMOS Properties**

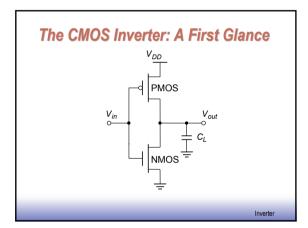

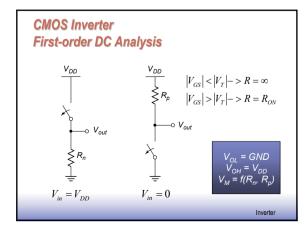

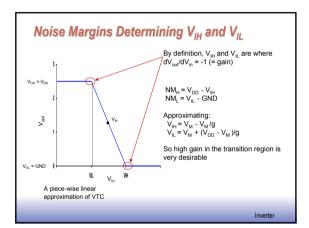

- $\Box$  Full rail-to-rail swing  $\Rightarrow$  high noise margins

- Logic levels not dependent upon the relative device sizes  $\Rightarrow$  transistors can be minimum size  $\Rightarrow$  ratioless

- $\label{eq:approx_state} \begin{array}{l} \square \mbox{ Always a path to } V_{dd} \mbox{ or GND in steady state } \Rightarrow \mbox{ low output impedance (output resistance in } k\Omega \mbox{ range}) \Rightarrow \mbox{ large fan-out (albeit with degraded performance)} \end{array}$

- □ Extremely high input resistance (gate of MOS transistor is near perfect insulator) ⇒ nearly zero steady-state input current

- $\hfill\square$  No direct path steady-state between power and ground  $\Rightarrow$  no static power dissipation

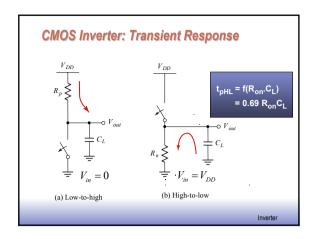

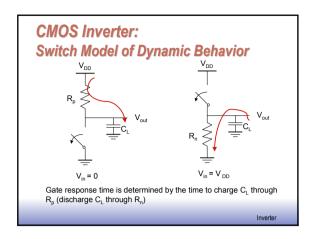

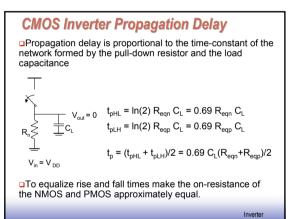

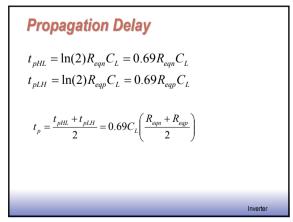

- Propagation delay function of load capacitance and resistance of transistors

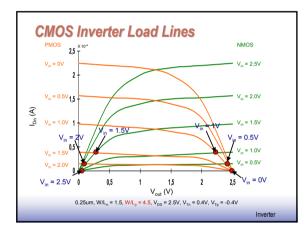

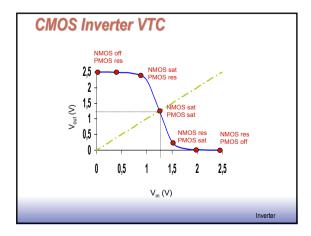

Inverter

Inverter

Voltage Transfer Characteristic

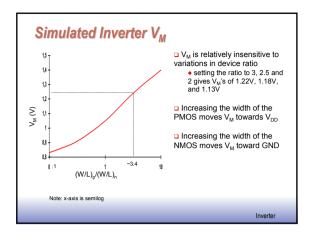

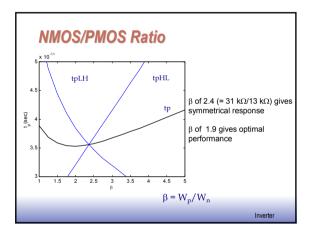

# Switching Threshold As a Function of Transistor Ratio

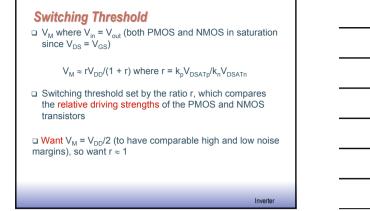

$$\begin{split} & \mathsf{V}_{\mathsf{M}} \text{ where } \mathsf{V}_{\mathsf{IN}} = \mathsf{V}_{\mathsf{OUT}} \text{ (both PMOS and NMOS in saturation since } \mathsf{V}_{\mathsf{GS}} = \mathsf{V}_{\mathsf{DS}} \text{)} \\ & \mathsf{Velocity-Saturation } \mathsf{V}_{\mathsf{DSAT}} < \mathsf{V}_{\mathsf{M}} - \mathsf{V}_{\mathsf{T}} \\ & \mathsf{I}_{\mathsf{Dn}} + \mathsf{I}_{\mathsf{Dp}} = \mathsf{0} \\ & k_{n} V_{\textit{DSATn}} \left( V_{\mathit{M}} - V_{\mathit{Tn}} - \frac{V_{\textit{DSATn}}}{2} \right) + k_{p} V_{\textit{DSATp}} \left( V_{\mathit{M}} - V_{\textit{DD}} - V_{\mathit{Tn}} - \frac{V_{\textit{DSATn}}}{2} \right) = \mathsf{0} \\ & \mathsf{V}_{\mathit{M}} = \frac{\left( V_{\mathit{Tn}} + \frac{V_{\textit{DSATn}}}{2} \right) + r \left( V_{\textit{DD}} + V_{\mathit{Tp}} + \frac{V_{\textit{DSATp}}}{2} \right) \\ & \mathsf{1} + r \\ & \mathsf{V}_{\mathit{M}} \approx \frac{r V_{\textit{DD}}}{k_{n} V_{\textit{DSATn}}} = \frac{\upsilon_{\textit{satp}} W_{p}}{\upsilon_{\textit{satn}} W_{n}} \\ & \mathsf{V}_{\mathit{M}} \approx \frac{r V_{\textit{DD}}}{1 + r}; V_{\textit{DD}} >> V_{\mathit{T}} + V_{\textit{DSAT}} \end{split}$$

5

### Electronique Numerique Integree

Switching Threshold As a

Function of Transistor Ratio

$$k_n V_{DSATn} \left( V_M - V_{Tn} - \frac{V_{DSATn}}{2} \right) + k_p V_{DSATp} \left( V_M - V_{DD} - V_{Tn} - \frac{V_{DSATn}}{2} \right) = 0$$

$$k = k' \frac{W}{L}$$

$$\frac{(W/L)_p}{(W/L)_n} = \frac{k'_n V_{DSATp} (V_M - V_{Tn} - V_{DSATn}/2)}{k'_p V_{DSATp} (V_{DD} - V_M + V_{Tp} + V_{DSATp}/2)}$$

Inverse

| Swit         | chin                | g Th    | reshc                 | old : E                                       | ixample                                   |

|--------------|---------------------|---------|-----------------------|-----------------------------------------------|-------------------------------------------|

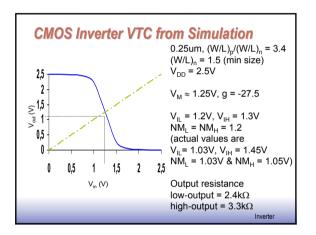

| 0.25µm       | СМОЗ                | 6       |                       |                                               |                                           |

| VDD=2        | .5V                 | 1       | L=0.25µn              | 1                                             | W=0.375µm                                 |

| NMOG         | V <sub>T0</sub> (V) |         | V <sub>DSAT</sub> (V) | k'(A/V <sup>2</sup> )<br>115.10 <sup>-6</sup> | $\lambda(V^{-1})$<br>0.06                 |

| NMOS<br>PMOS | 0.43                | -0.4    | 0.63                  | -30.10*                                       |                                           |

|              |                     |         |                       |                                               | $\frac{43 - 0.63/2)}{0.4 - 1.0/2)} = 3.5$ |

| (            | W/L) <sub>p</sub> = | = 3.5 > | (1.5 = 5              | .25 for a                                     | V <sub>M</sub> of 1.25V                   |

|              |                     |         |                       |                                               | Inverter                                  |

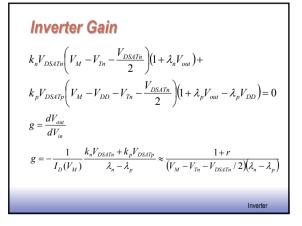

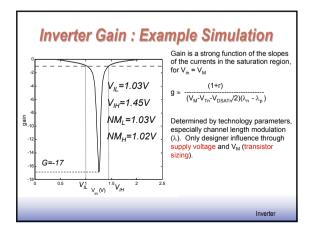

|                                    |                  |        |                          | k'(A/V <sup>2</sup> ) |                                                         |

|------------------------------------|------------------|--------|--------------------------|-----------------------|---------------------------------------------------------|

| NMOS<br>PMOS                       | 0.43             | -0.4   | 0.63                     |                       | 0.06                                                    |

| g = <u>1</u>                       | 1.5×             | 115×10 | $^{-6} \times 0.63 + 1.$ | 5×3.4×30>             | $\frac{10^{-6} \times 1.0}{10^{-6} \times 1.0} = -27.5$ |

| $g = \frac{1}{59 \times 10^{-10}}$ | 10 <sup>-6</sup> |        | 0.06+                    | 0.1                   | =-27.5                                                  |

|                                    |                  |        |                          |                       |                                                         |

|                                    |                  |        |                          |                       |                                                         |

10

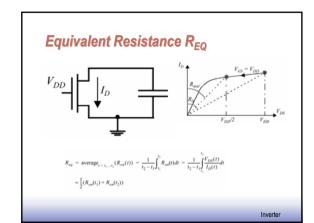

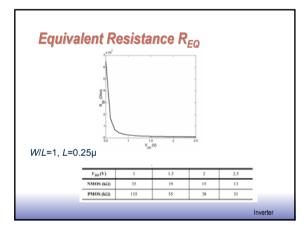

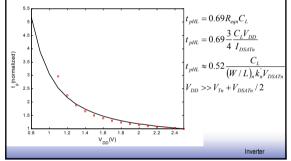

Equivalent Resistance R<sub>EQ</sub> Solving the integral:  $R_{eq} = \frac{1}{-V_{DD}/2} \int_{V_{DD}}^{V_{DD}/2} \frac{V}{I_{DSAT}(1+\lambda V)} dV = \frac{3}{4} \frac{V_{DD}}{I_{DSAT}} \left(1 - \frac{7}{9} \lambda V_{DD}\right)$ with appropriately calculated Idsat  $I_{DSAT} = k \frac{W}{L} \left( (V_{DD} - V_T) V_{DSAT} - \frac{V_{DSAT}^2}{2} \right)$ Averaging resistances:  $R_{eq} = \frac{1}{2} \left( \frac{V_{DD}}{I_{DS4T}(1 + \lambda V_{DD})} + \frac{V_{DD}/2}{I_{DS4T}(1 + \lambda V_{DD}/2)} \right) = \frac{3}{4} \frac{V_{DD}}{I_{DS4T}} \left( 1 - \frac{5}{6} \lambda V_{DD} \right)$ Inverter

Delay As a Function of V<sub>DD</sub>

$\square To see how a designer can optimize the delay of a gate have to expand the <math display="inline">R_{eq}$  in the delay equation

#### **Design for Performance**

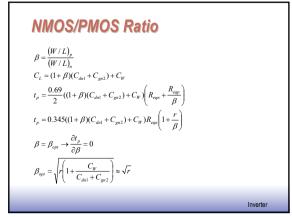

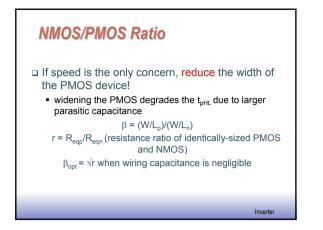

Reduce C<sub>1</sub>

- internal diffusion capacitance of the gate itself

- keep the drain diffusion as small as possible

- interconnect capacitance

- fanout

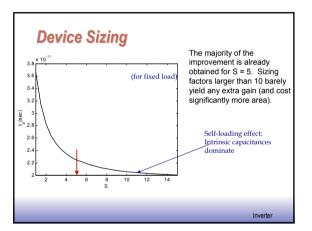

- Increase W/L ratio of the transistor

- the most powerful and effective performance optimization tool in the hands of the designer

- watch out for self-loading! when the intrinsic capacitance dominates the extrinsic load

- □ Increase V<sub>DD</sub>

- can trade-off energy for performance

- increasing  $V_{\mbox{\scriptsize DD}}$  above a certain level yields only very minimal improvements

Inverter

- reliability concerns enforce a firm upper bound on  $\mathrm{V}_{\mathrm{DD}}$

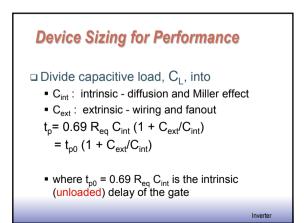

#### **Device Sizing for Performance**

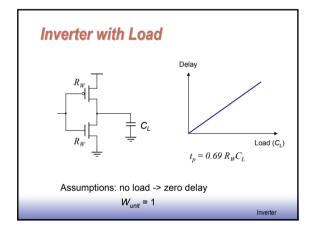

□ Widening both PMOS and NMOS by a factor S reduces  $R_{eq}$  by an identical factor ( $R_{eq} = R_{ref}/S$ ), but raises the intrinsic capacitance by the same factor ( $C_{int} = SC_{iref}$ )

$$t_p = 0.69 R_{ref} C_{iref} (1 + C_{ext}/(SC_{iref}))$$

- $= t_{p0}(1 + C_{ext}/(SC_{iref}))$ •  $t_{p0}$  is independent of the sizing of the gate; with no load the drive of the gate is totally offset by the increased capacitance

- any S sufficiently larger than  $(C_{\text{ext}}/C_{\text{int}})$  yields the best performance gains with least area impact

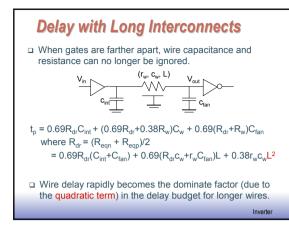

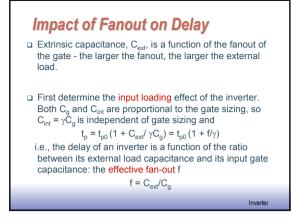

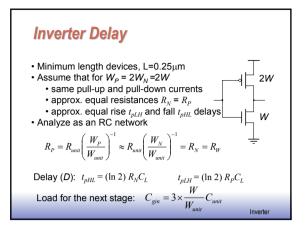

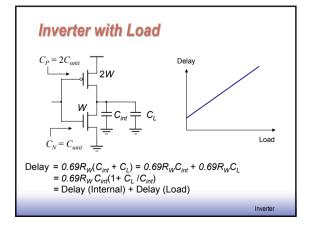

**Delay Formula** Delay ~  $R_W (C_{int} + C_L)$  $t_p = 0.69 R_W C_{int} (1 + C_L / C_{int}) = t_{p0} (1 + f / \gamma)$  $\begin{array}{l} C_{int} = \gamma C_g \mbox{ with } \gamma \approx 1 \\ f = C_t / C_g \mbox{-} \mbox{effective fanout} \\ R = R_{unit} / W \ ; \ C_{int} = W C_{unit} \\ t_{p0} = 0.69 R_{unit} C_{unit} \end{array}$ Inverter

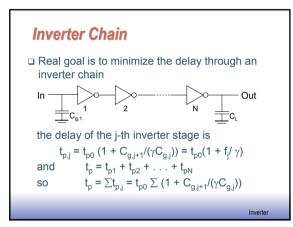

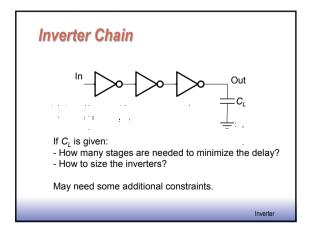

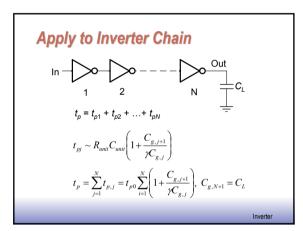

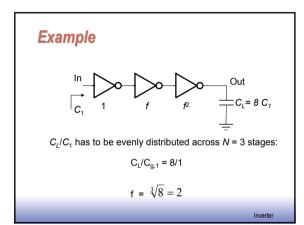

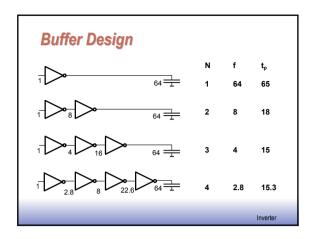

## **Optimal Tapering for Given N** Delay equation has N - 1 unknowns, $C_{g,2} - C_{g,N}$

Minimize the delay, find *N* - 1 partial derivatives  $\partial t_p / \partial C_{g,j} = 0$

Result:  $C_{g,j+1}/C_{g,j} = C_{g,j}/C_{g,j-1}$

Size of each stage is the geometric mean of two neighbors

$$C_{g,j} = \sqrt{C_{g,j-1}C_{g,j+1}}$$

- each stage has the same effective fanout  $(C_{out}/C_{in})$

each stage has the same delay

#### **Optimum Delay & Number of Stages**

When each stage is sized by *f* and has same eff. fanout *f*.

$$f^N = F = C_L / C_{gin,1}$$

Effective fanout of each stage:

$f = \sqrt[N]{F}$

$$t_p = Nt_{p0} \left( 1 + \sqrt[N]{F} / \gamma \right)$$

The relationship between  $t_{\rm p}$  and F is linear for one inverter, square root for two, etc.

١

Inverter

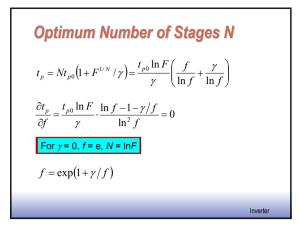

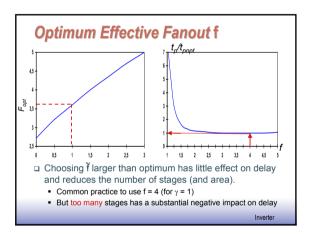

#### **Optimum Number of Stages N**

What is the optimal value for N given

$$f^{N} = F = C_{L} / C_{gin,1} \qquad t_{p} = Nt_{p0} \left( 1 + \sqrt[N]{F} / \gamma \right)$$

- if the number of stages is too large, the intrinsic delay of the stages becomes dominate

- if the number of stages is too small, the effective fanout of each stage becomes dominate

For a given load,  $C_{L}$  and given input capacitance  $C_{in}$ Find optimal sizing f

$$C_L = F \cdot C_{in} = f^N C_{in}$$

with  $N = \frac{\ln F}{\ln f}$

| F | (γ = 1) | Unbuffered | Two Stage<br>Chain | Opt. Inverter<br>Chain |

|---|---------|------------|--------------------|------------------------|

|   | 10      | 11         | 8.3                | 8.3                    |

|   | 100     | 101        | 22                 | 16.5                   |

|   | 1,000   | 1001       | 65                 | 24.8                   |

| 1 | 0,000   | 10,001     | 202                | 33.1                   |

21