# Introduction aux systèmes VLSI

---

Master IGIS

Spécialité Microélectronique

Richard GRISEL

Université de Rouen

# Plan de l'exposé

- L 'apparition des circuits intégrés

- La fabrication des puces

- Critères d 'évolution

- VLSI « Design Flow »

- Conception Hiérarchique

- Concepts de Regularité, Modularité and Localité

- Techniques de conception VLSI

# L'apparition des circuits intégrés

- Au fur et à mesure des progrès technologiques, le nombre de transistors augmente dans les ordinateurs pour réaliser des fonctions de plus en plus complexes. Le nombre des connexions pour les relier augmente aussi, d'où un risque de panne important. De nouveau, le développement de l'électronique et de l'informatique est freiné.

- Les recherches s'orientent alors vers une nouvelle piste : supprimer les connexions. En 1959, un véritable saut technologique est réalisé avec la mise au point de la technologie "planar". Cette technologie consiste à intégrer plusieurs transistors et leurs connexions à la surface d'un même cristal de silicium. Ces différents éléments sont connectés grâce à des couches minces métalliques gravées. Il n'y a plus de problèmes de soudure. Les différents composants sont d'une taille de l'ordre du micron. On obtient alors ce que l'on appelle un circuit intégré.

- La **microélectronique** est née.

- Le circuit intégré réunit plusieurs transistors, diodes, résistances et condensateurs et les interconnexions entre tous ces éléments sur une seule plaque de silicium.

- En 1961, le premier circuit intégré comporte 6 composants. En 1966, les circuits intégrés contiennent 100 composants. Le premier microprocesseur\*\* Intel possède 2250 transistors sur une surface de cm<sup>2</sup>. Un microprocesseur 16 bits, en 1976, comprenait 100 000 composants.

- Aujourd'hui, un circuit intégré est un morceau de plaque de silicium de 10 à 300 mm<sup>2</sup> pouvant comporter plusieurs dizaines de millions de composants. Ce circuit intégré est appelé "puce".

## ■ **Les transistors actuels**

- Les premiers transistors sont trop volumineux et consomment beaucoup d'énergie. Ces difficultés contribuent, dans les années 70, au développement d'une nouvelle famille de dispositifs appelés transistors MOS (métal, oxyde, semi-conducteur). Cette nouvelle technologie va permettre l'augmentation rapide du nombre de composants par circuit intégré et par conséquence l'explosion de la micro-informatique.

- La plupart des transistors actuels sont des MOS. Un transistor MOS comprend un émetteur d'électrons (la source), un contrôleur (la grille) et un récepteur (le drain). Ces transistors sont fabriqués par multiples dépôts successifs de différentes couches de matériaux (conducteurs, semi-conducteurs et isolants).

- Les semi-conducteurs et conducteurs constituent les chemins que les électrons peuvent suivre. Les matériaux non conducteurs isolent les conducteurs entre eux, ils canalisent les flux d'électrons, c'est-à-dire courant électrique.

- Le cristal de silicium est le semi-conducteur le plus utilisé. Or, la disposition des atomes de silicium est très ordonnée dans un cristal. Ceux-ci sont rangés en colonnes régulièrement disposées. Dans cette organisation parfaite, aucun électron n'est libre, donc le courant ne passe pas, sauf si des ions étrangers viennent perturber ce bel arrangement en apportant un surplus ou un manque d'électrons ("trous" positifs).

- Alors, le cristal de silicium est dopé et le courant peut passer. Cette capacité du silicium à accueillir des impuretés en quantité limitée est utilisée pour déterminer les flux d'électrons qui emprunteront les chemins tracés. L'oxyde de silicium sert d'isolant entre les chemins. La plupart des transistors actuels sont des MOS. Ils sont fabriqués par multiples dépôts successifs de différentes couches de matériaux (conducteurs, semi-conducteurs et isolants).

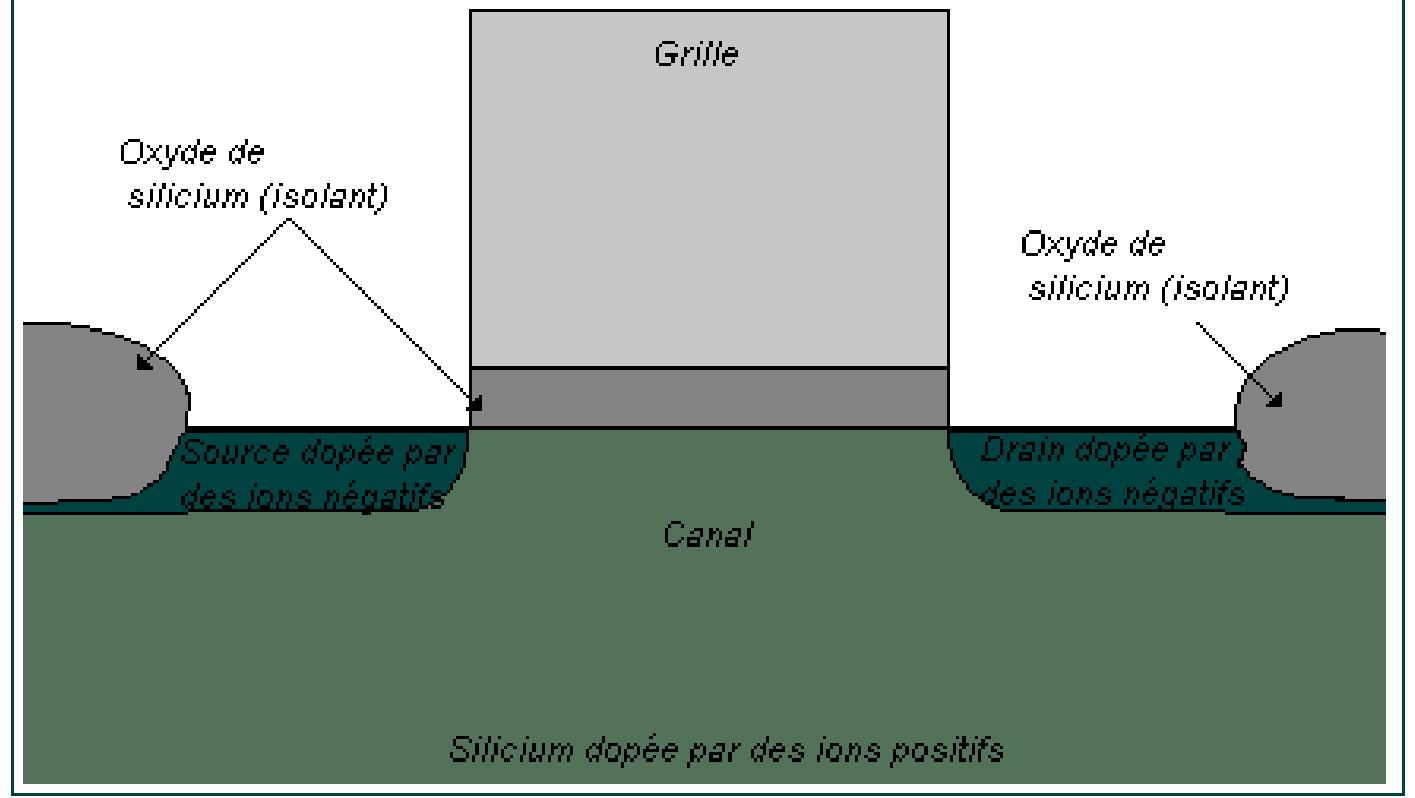

# Le principe de fonctionnement d'un transistor MOS

- Malgré sa taille microscopique, le transistor MOS est un système parfaitement structuré. Sur un substrat dopé par des ions positifs (par exemple le bore), la source et le drain sont dopés négativement (avec de l'arsenic, par exemple). Dans d'autres types de transistors MOS, c'est l'inverse. Le substrat peut être dopé négativement et la source et le drain positivement. Lorsque la grille est mise sous tension positive, les "trous positifs" du canal se remplissent d'électrons, ce qui crée un canal pour les électrons entre la source et le drain. Si le drain est mis sous tension, un courant électrique\* pourra atteindre la source via le canal. La tension appliquée à la grille va donc contrôler la largeur du canal qui lui-même va déterminer les modalités de passage du courant entre le drain et la source.

- Une couche d'oxyde (appelé oxyde de grille) isole la grille du substrat.

# Vue en coupe d'un transistor MOS

*Coupe d'un type de transistor MOS*

# La fabrication des puces

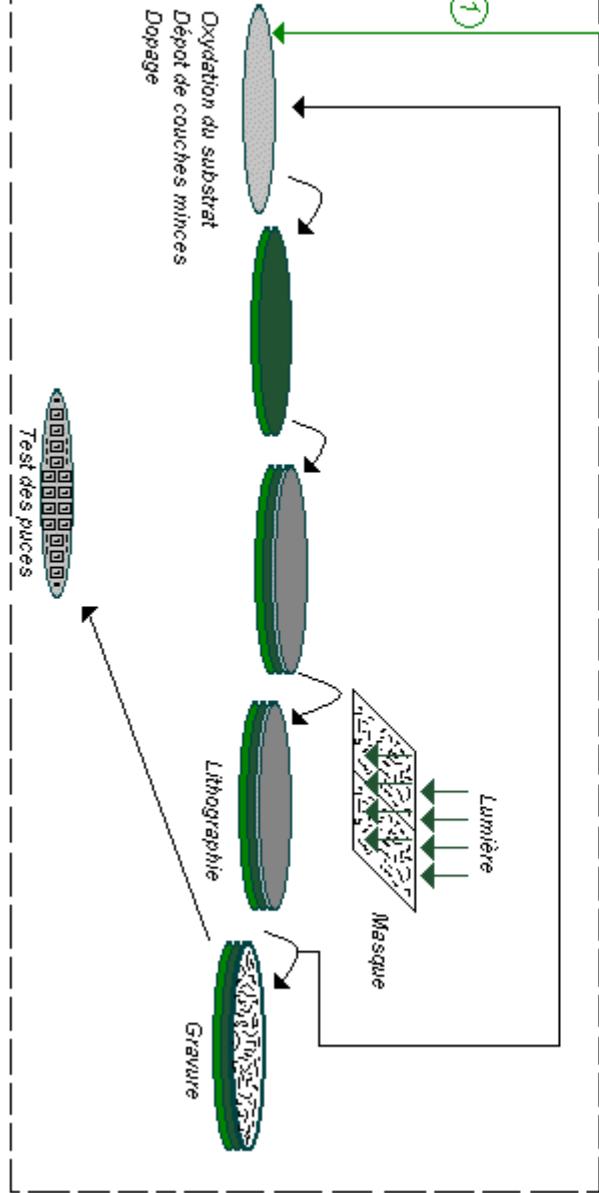

Les techniques de fabrication des circuits intégrés sont très complexes. Il s'agit en effet de réaliser sur une surface de quelques mm<sup>2</sup> et une épaisseur de quelques microns un assemblage de plusieurs milliers de composants et les interconnexions entre tous ces éléments.

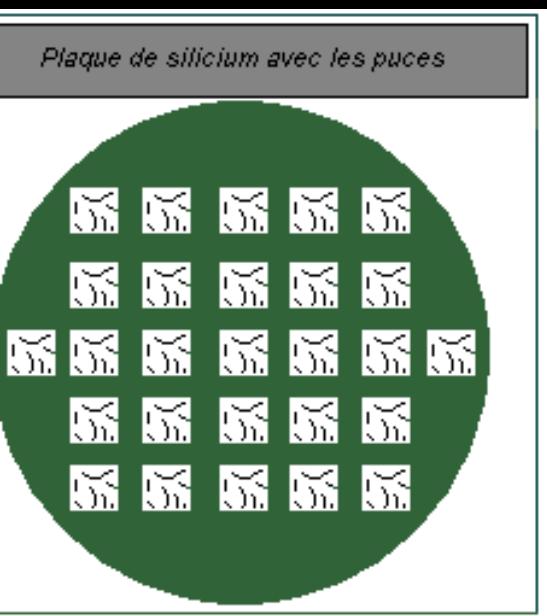

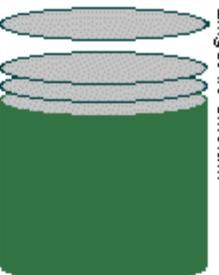

Le matériau de départ est une tranche (disque) très fine de silicium dont le diamètre ne cesse de croître. Il est couramment de dix centimètres de diamètre mais peut atteindre des tailles de l'ordre de 20 cm.

Ce disque de silicium subit près d'une centaine de traitements différents : dépôt de couches minces isolantes ou conductrices, micro-gravure, attaque chimique, recuit thermique approprié, dopage par implantation d'atomes ...

Plusieurs circuits intégrés sont fabriqués en même temps sur une plaque de silicium et le procédé de fabrication traite des lots de 50 à 100 tranches de silicium.

Lorsque l'ensemble des traitements est effectué, la tranche de silicium qui regroupe une à plusieurs centaines de fois le même circuit intégré élémentaire est découpée en pastilles. Le circuit intégré nu est très fragile. Pour être utilisée, chaque pastille ou puce est montée dans un boîtier céramique ou plastique muni de pattes de connexions. Une fois encapsulée, chaque puce est alors contrôlée individuellement et celles qui ont un fonctionnement défectueux ou qui s'écartent trop des spécifications attendues sont rejetées.

Le rendement d'une chaîne de fabrication est l'une des mesures principales de la qualité d'une filière technologique. Par exemple, pour des circuits de complexité moyenne, 40 % à 60 % de ceux-ci ont un fonctionnement correct.

# La conception assistée par ordinateur

Comme un architecte, le concepteur de puces doit d'abord dessiner un plan. Toute proportion gardée, c'est comme essayer de faire rentrer le plan d'une grande ville (Grenoble par exemple) dans un cm<sup>2</sup>. Autant dire que sans l'aide de la conception assistée par ordinateur, la mission serait impossible.

Après avoir déterminé les fonctions de la puce, le concepteur puise dans des bibliothèques informatisées les millions d'éléments qui vont constituer le circuit.

Comme dans un puzzle géant, il doit d'abord chercher à arranger les pièces les unes par rapport aux autres, puis dessiner les chemins qui vont les relier.

Avant de lancer la fabrication, il simule sur ordinateur le fonctionnement de sa puce. Si tout va bien, il passe alors les plans et leur mode d'emploi au secteur production.

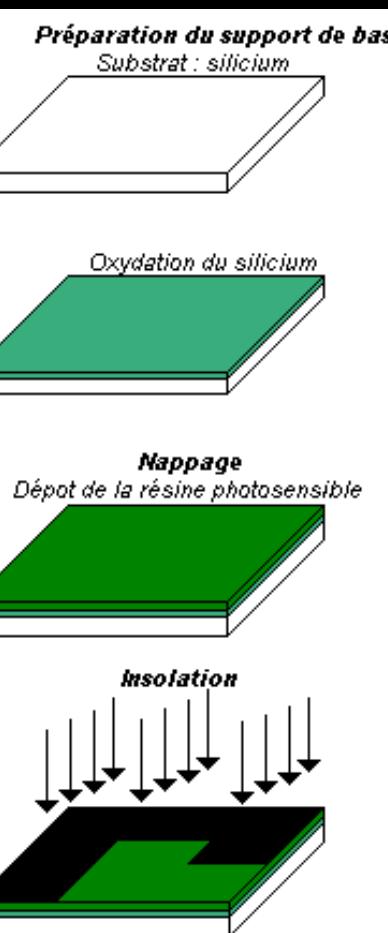

# La photolithographie

L'un des traitements clefs de la fabrication d'un circuit intégré est la photolithographie. Ce procédé permet la construction des chemins pour les électrons et les barrières isolantes pour les séparer.

Pour préparer le support, on chauffe la plaquette de silicium à plus de 1000°C. Comme pour la rouille du fer, il se passe une réaction chimique à la surface : l'oxydation. La plaque est alors entièrement recouverte d'une fine couche isolante d'oxyde de silicium. Le support est maintenant prêt. La résine photosensible\* est répandue uniformément sur toute la surface du support. Si on compare la photolithographie à la photographie, la résine joue le rôle de la pellicule. Une fois recouverte de résine, la tranche de silicium est soumise à une lumière visible ou à un rayonnement ultraviolet (UV) à travers un masque représentant le motif recherché. Les rayonnements impressionnent ("insolent") la résine. Cela permet l'insolation.

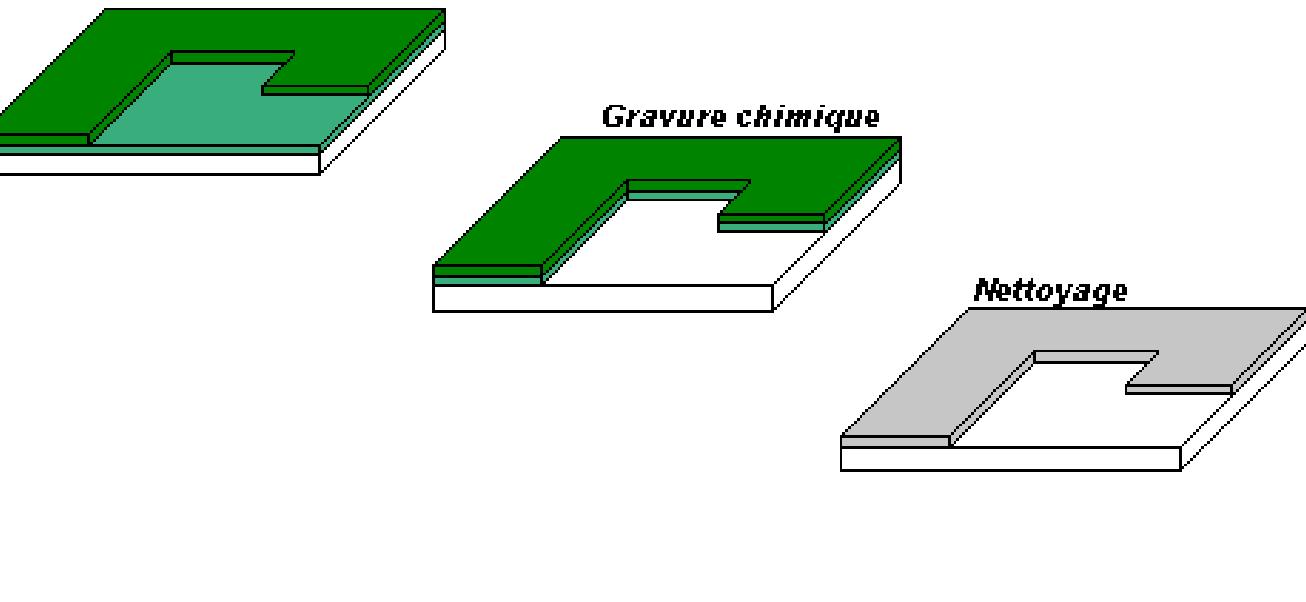

### *Elimination de la résine insolée*

Après avoir éliminé la résine insolée, les zones non protégées celle-ci sont gravées par attaque acide. Le silicium est donc mis à selon les contours du masque. Les restes de résine sont éliminés à l'aide solvant. Le support est prêt pour l'étape suivante.

La microlithographie est difficile à réaliser puisque les motifs souvent une dimension inférieure à un micron. De plus, l'obtention d'un circuit intégré nécessite de dix à quatorze gravures dont la superposition peut être réalisée, pour certains circuits, avec une précision de l'ordre de 0,35 mm.

# Le dopage

Le dopage d'un semi-conducteur, qui consiste à introduire des ions perturbateurs (arsenic, bore, phosphore...) dans le cristal de silicium pour modifier sa conductivité, peut être réalisé soit par chauffage dans un four très chaud (1200 °C) en présence d'un gaz dopant, soit de plus en plus souvent par bombardement d'ions à travers un masque.

## La salle blanche

Les puces ne supportent pas les poussières.

A l'échelle d'une puce, un grain de poussière représente un rocher qui bouche les chemins creusés pour la circulation des électrons. Pour cette raison les lieux de fabrication des puces, les salles blanches, sont extrêmement propres. L'eau, l'air, les produits chimiques, de même que l'humidité et la température de la salle blanche doivent être rigoureusement contrôlés. Les opérateurs en salle blanche n'échappent pas à la règle. Ils portent une combinaison spéciale qui retient les particules organiques et les poussières. En effet, l'homme est la principale source de micro-poussières : 500 000 particules sont dégagées par une chevelure lors d'un mouvement de tête. L'haleine d'un fumeur contient encore 20 000 particules à chaque expiration trois heures après sa dernière cigarette.

## Fabrication d'une puce

Préparation du substrat :

Découpage de tranches

(ou disques) et polissage

objectif de la microélectronique est de mettre le maximum de composants électroniques (transistors) dans le minimum de volume. Pourquoi ?

## Pour accéder à de nouveaux services

La microélectronique, en intégrant davantage de fonctions sur une même puce, permet une économie dans le volume du système. Depuis 1950, la surface d'un transistor a été réduite d'un facteur supérieur à 10 000. Le coût des circuits diminue d'un facteur deux à peu près tous les 18 mois, accompagné par un accroissement important de leurs performances. Dans le même temps, on augmente la fiabilité de l'ensemble du système et les performances des dispositifs.

Cette évolution permet à un large public d'accéder à des services performants, moins chers et souvent nouveaux : par exemple, le Mini-ordinateur, le téléphone portable, la télévision numérique, le disque compact, les baladeurs...

## Pour accéder à des calculs complexes

En réduisant la taille des équipements informatiques et leur coût, on peut en ajouter de nouveaux services. Dans le domaine du calcul scientifique, l'augmentation de rapidité permet d'effectuer des calculs plus volumineux et de mieux simuler les phénomènes physiques ou les options technologiques étudiées. La miniaturisation permet, en effet, d'accroître la rapidité des calculs.

Mais il existe une limite à la vitesse de calcul. L'information ne peut aller plus vite que la vitesse de l'impulsion électrique. Pour pouvoir augmenter la rapidité du calcul, il faut réduire les distances géométriques... et empiler au maximum de données d'information dans un minimum d'espace pour les rapprocher.

En résumé, la réduction du volume physique des systèmes microélectroniques a permis :

- ☞ la réduction des coûts,

- ☞ l'augmentation des performances des dispositifs,

- ☞ - l'accès à de nouveaux services,

- ☞ - la démocratisation de ces services,

- ☞ la rapidité de calcul permettant de mettre à la disposition des chercheurs etingénieurs des outils plus performants.

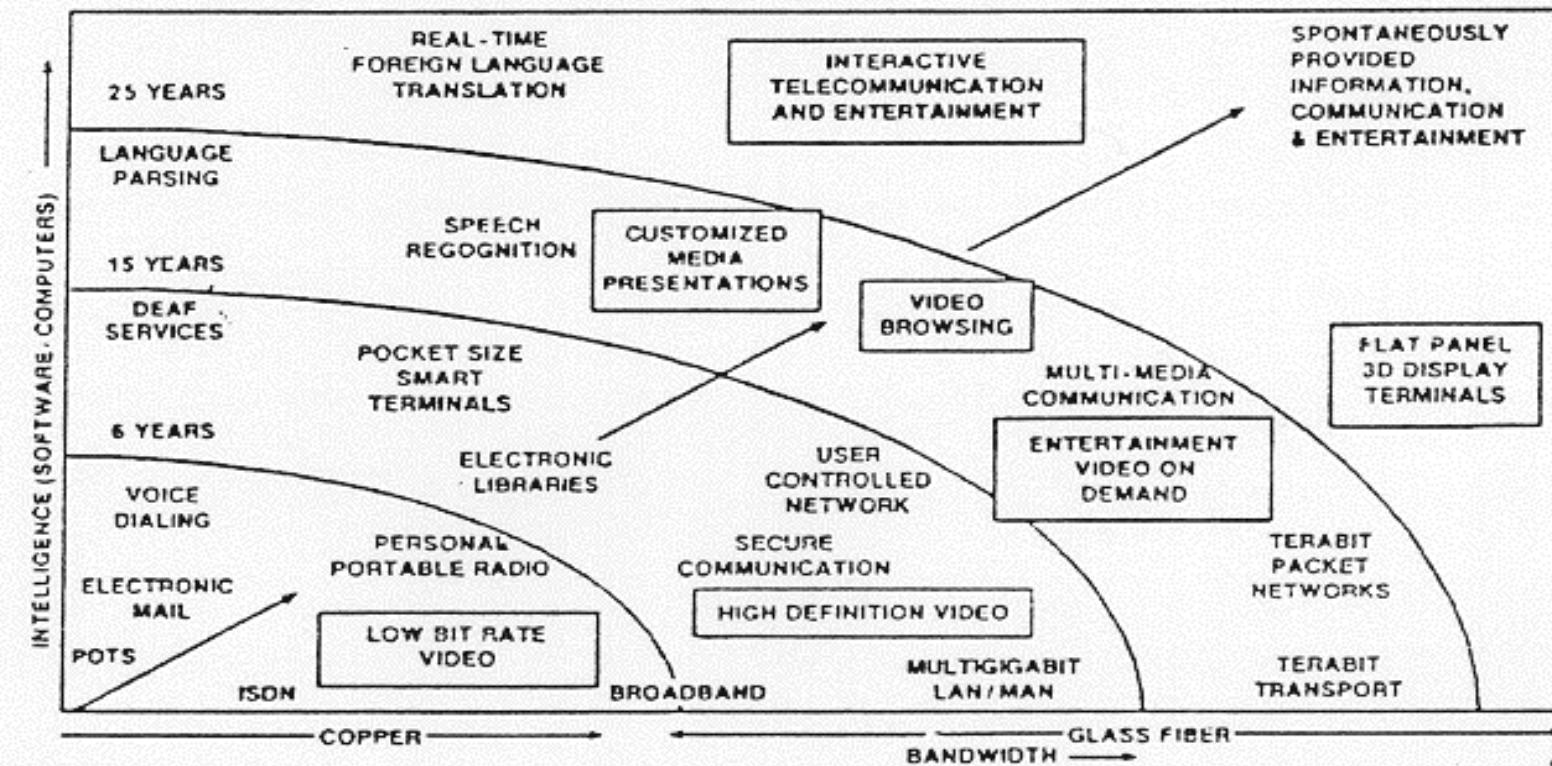

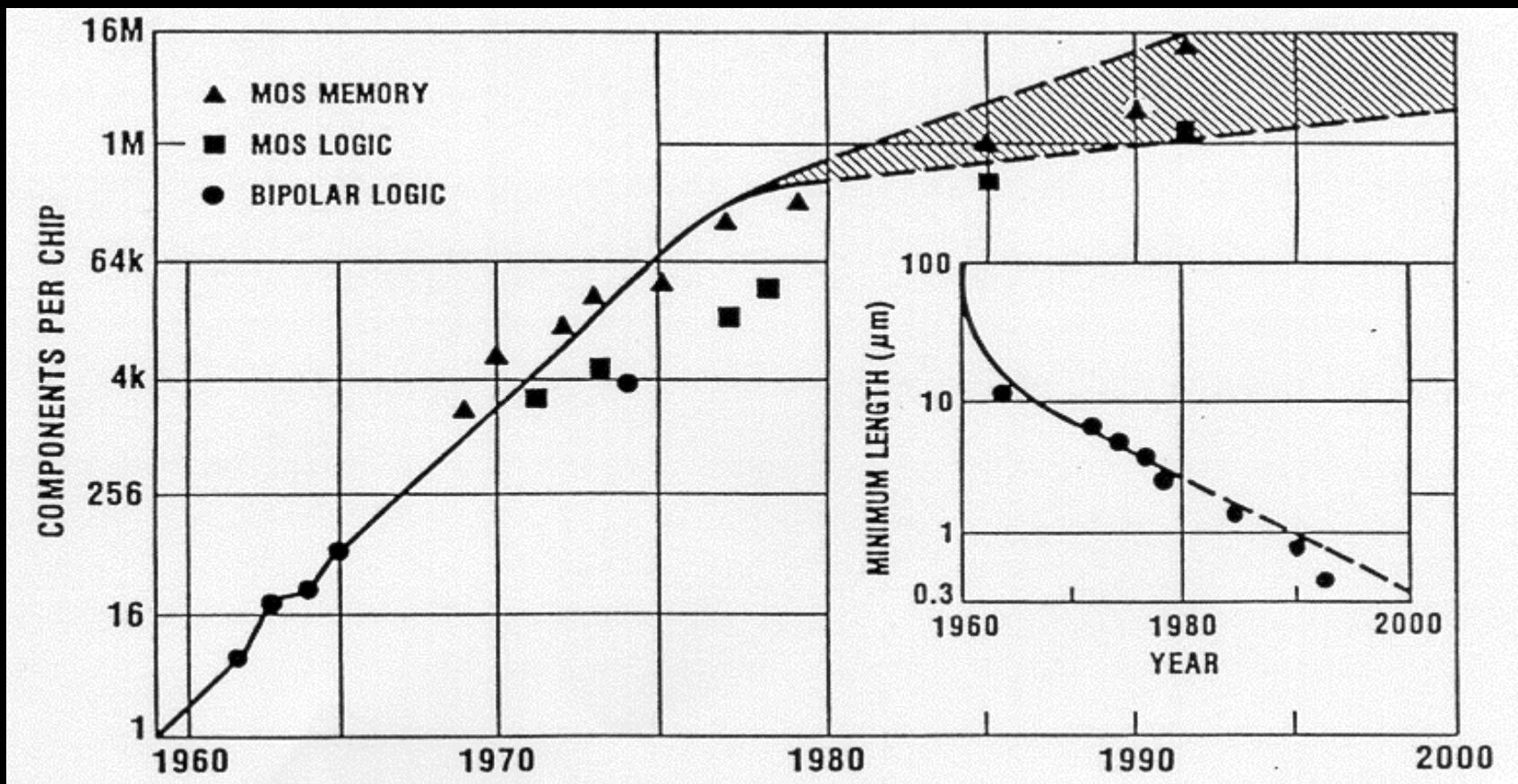

# Critères d'évolution

- Forte croissance depuis 1980 due à l 'avancé de technologies micro-électroniques

- Les applications des circuits intégrés (VLSI) croissent de manière drastique (télécommunications électronique grand public)

- Les technologies émergentes (vidéo - téléphonie mobile) sont fortement demandeuses

- Information et communication s 'orientent vers la personnalisation et donc vers l 'intelligence, la portabilité, la mobilité

# Indicateur « intelligence-Bande passante »

Source: Bellcore

# Evolution de la complexité

|                                      | Année | Blocs logiques*  |

|--------------------------------------|-------|------------------|

| Single transistor                    | 1959  | less than 1      |

| Unit logic (one gate)                | 1960  | 1                |

| Multi-function                       | 1962  | 2 - 4            |

| Complex function                     | 1964  | 5 - 20           |

| Medium Scale Integration             | 1967  | 20 - 200 (MSI)   |

| Large Scale Integration              | 1972  | 200 - 2000 (LSI) |

| Very Large Scale Integration (VLSI)  | 1978  | 2000 - 20000     |

| Ultra Large Scale Integration (ULSI) | 1989  | 20000 - ?        |

\* 1 bloc logique (10 à 100 transistors - Pentium (6 millions)

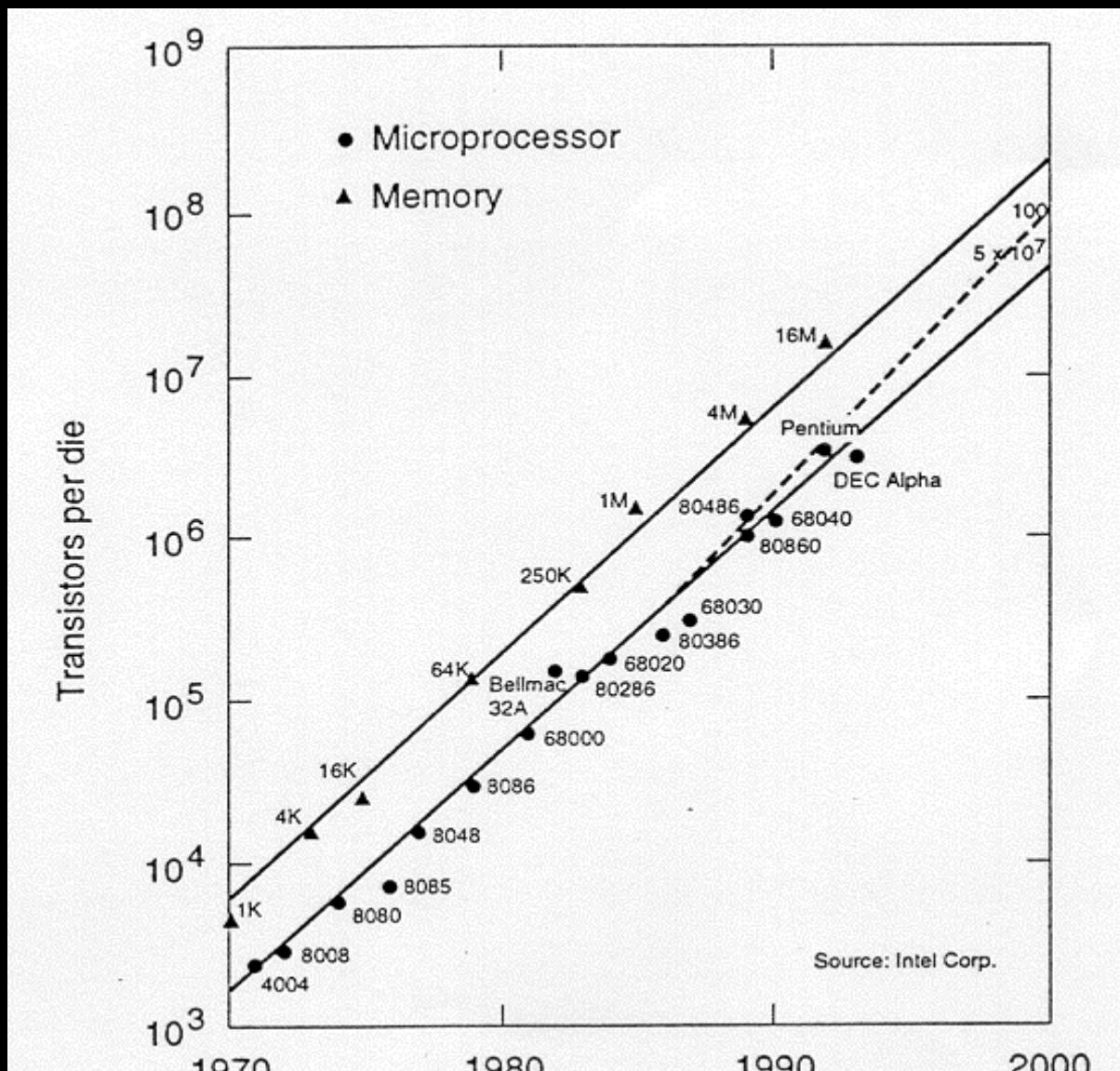

# La croissance de la complexité est quasi-exponentielle

On veut moins de consommation, de surface, de test système

On veut plus de fiabilité, de vitesse, de réduction des coûts et du « time-to-market »

# Distinction mémoires - circuits logiques complexes (DSP - $\mu$ P)

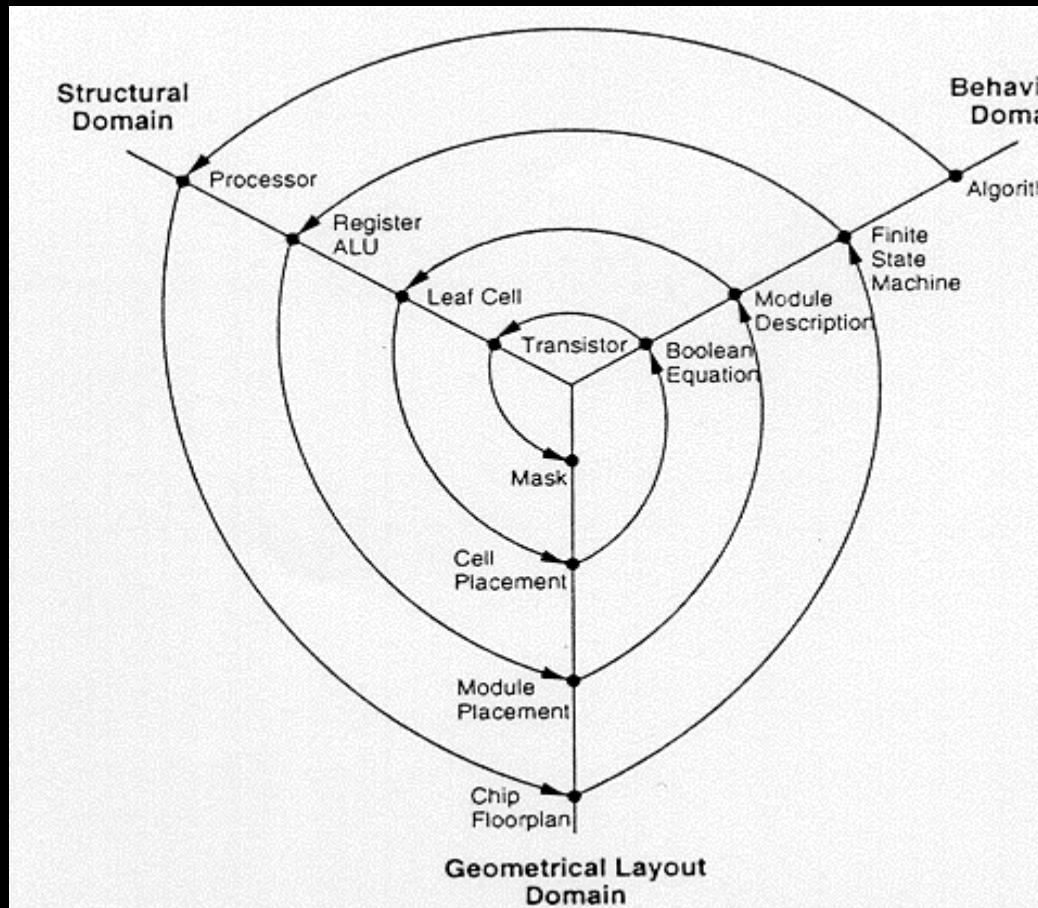

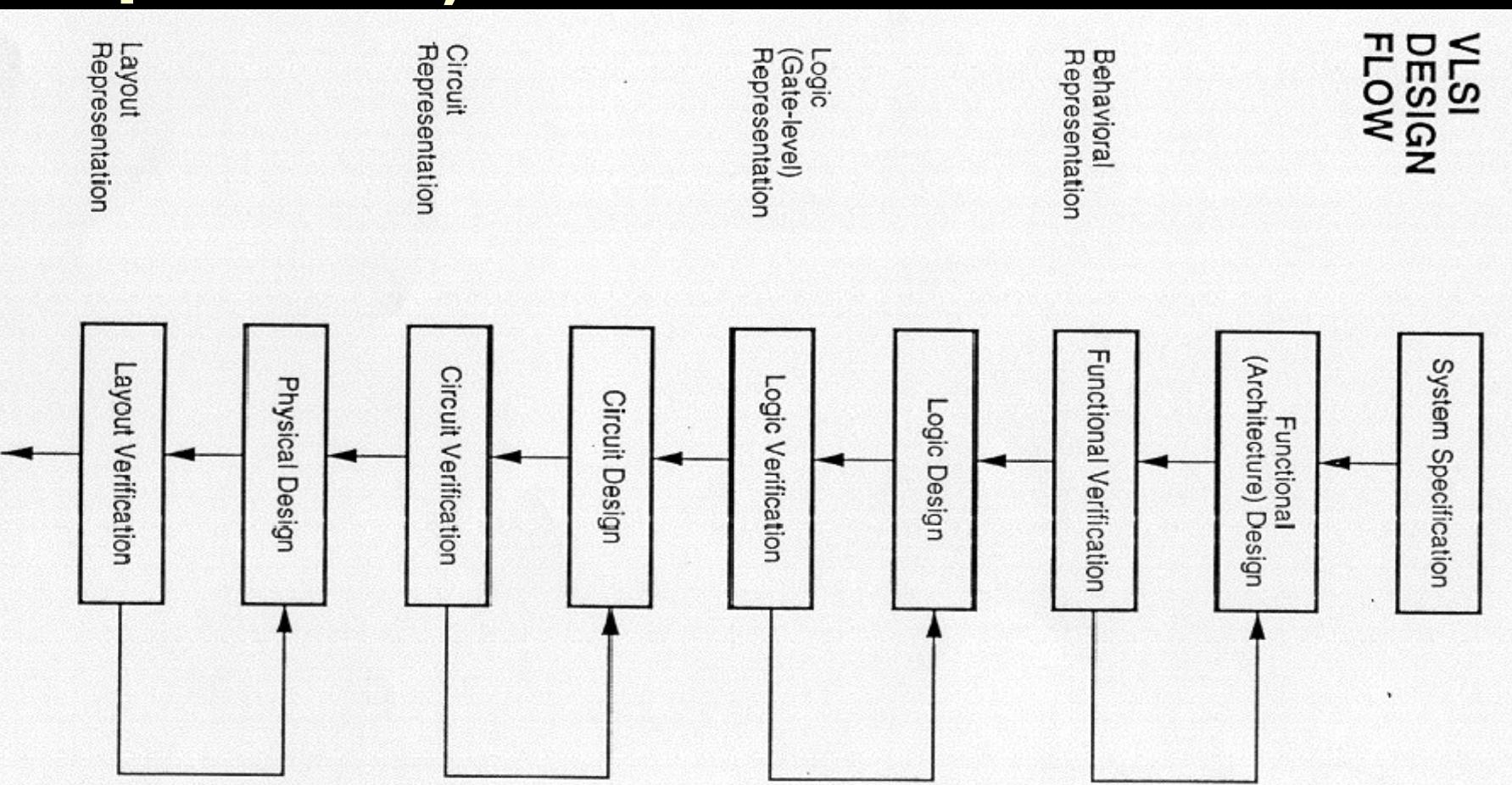

# VLSI « Design Flow » Y-chart

3 domaines

- ◆ Comportemental

- ◆ Structurel

- ◆ Géométrique

- ◆ Introduit par D. Gajski

# Design Flow simplifié (Bottom-up Top-Down)

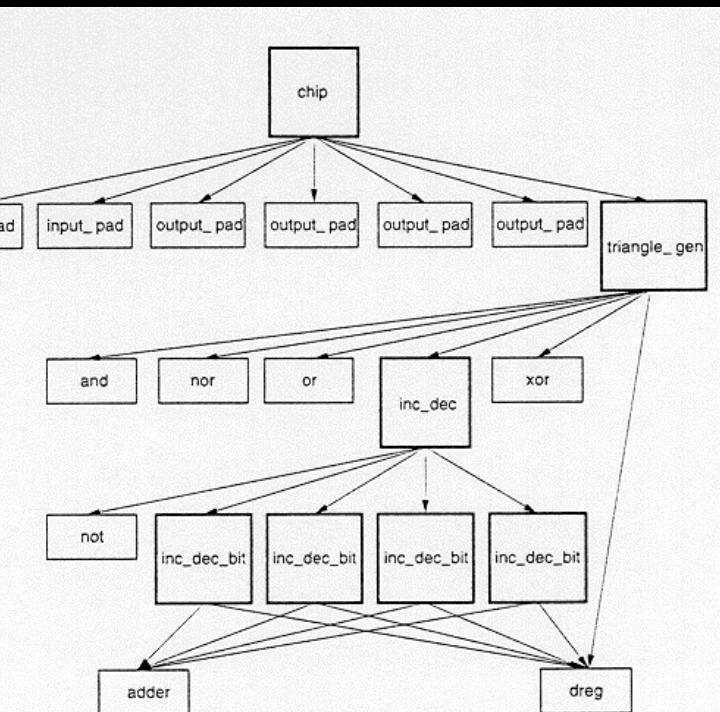

# Conception Hiérarchique

- Hiérarchie : division d 'un module en sous-modules et ainsi de suite jusqu 'à obtenir un module « exploitable »

- On peut oser le parallèle avec le logiciel en terme de sous-programmes etc..

- Pour les 3 domaines (section 2) on peut envisager une structure hiérarchique, cependant il est préférable de l 'envisager en terme d 'imbrication pour les 3 domaines

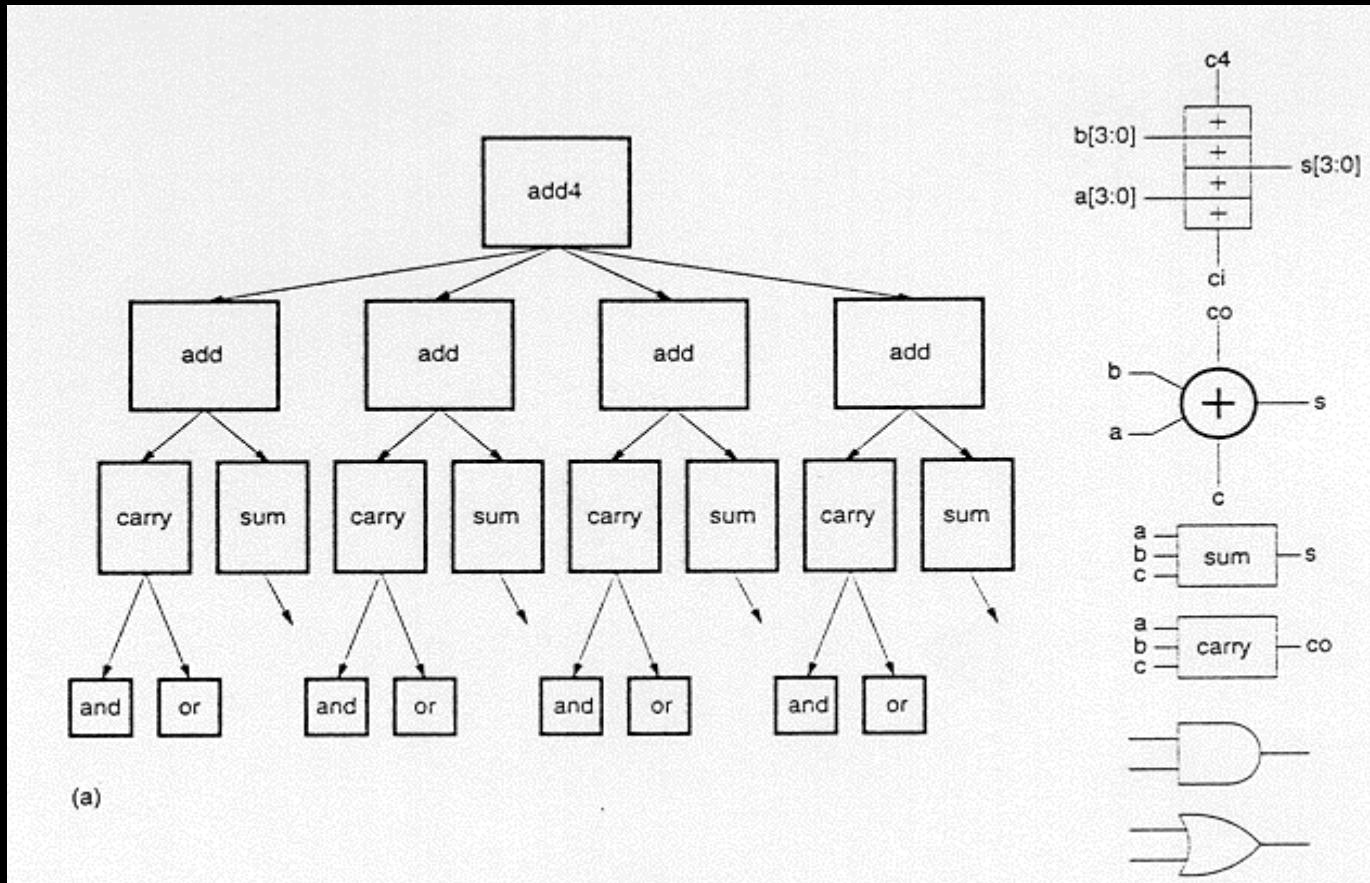

# Exemple de hiérarchie structurelle (additionneur 4 bits CMOS)

- Décomposition ADD  $\Rightarrow$  CARRY-SUM  $\Rightarrow$  Opérateurs

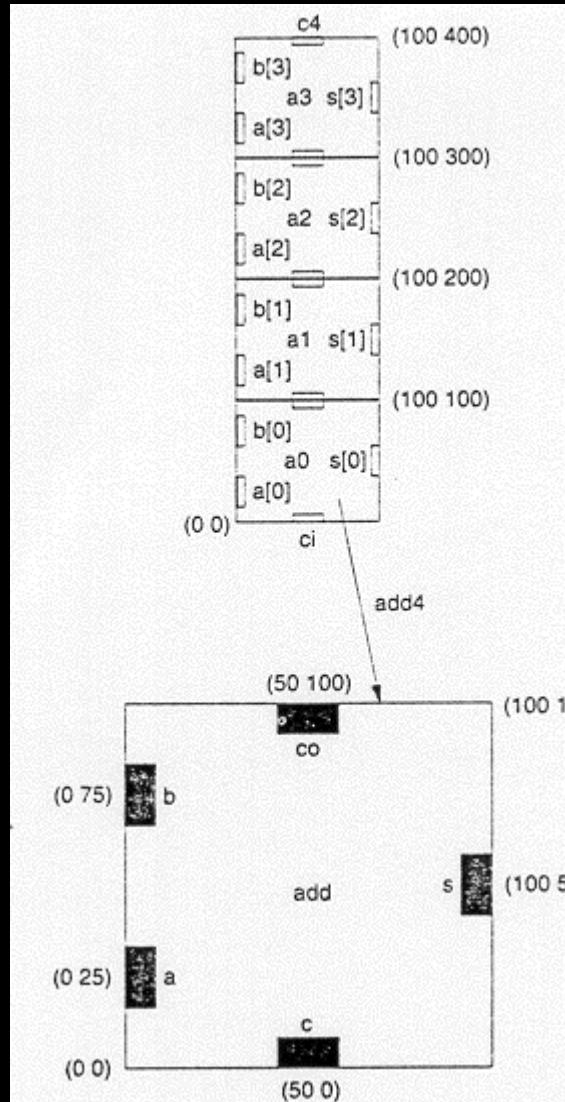

# Hiérarchie géométrique

- Estimation de la taille de la cellule est importante pour le masque final

- Utilisation d 'interconnexions entre blocs élémentaires (carry) sans routage extérieur

- Le « floorpan » (plan au sol) est dimensionné dans la technologie

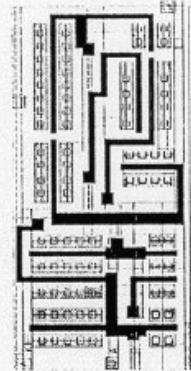

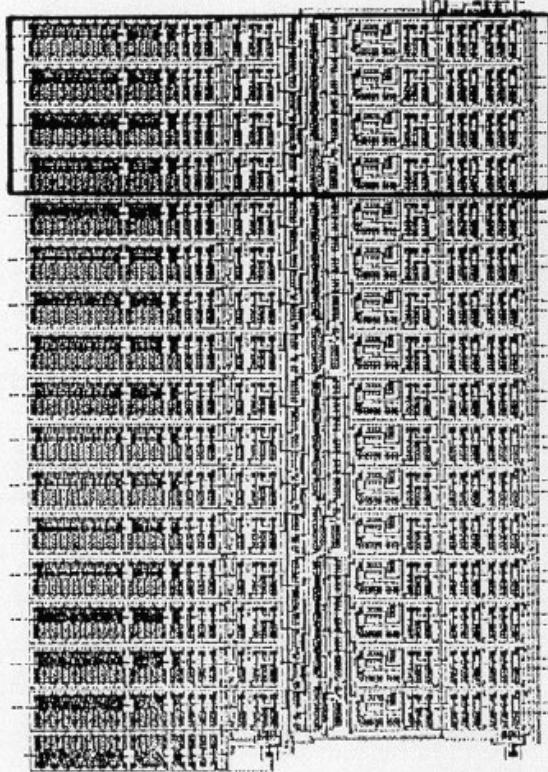

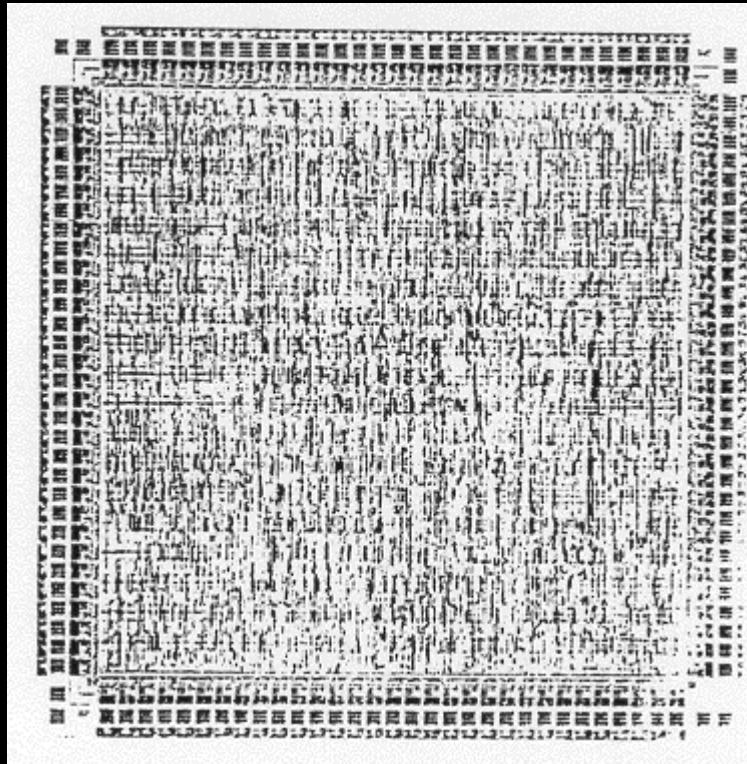

# Full-custom 16 bits dynamic CMOS adder

Output buffer/latch

circuit layout

Manchester-carry

circuit layout

Carry/propagate

circuit layout

4-bit adder with

Manchester-carry

16-bit adder

complete layout

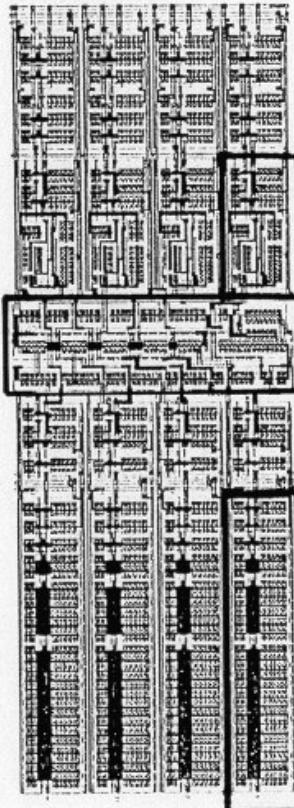

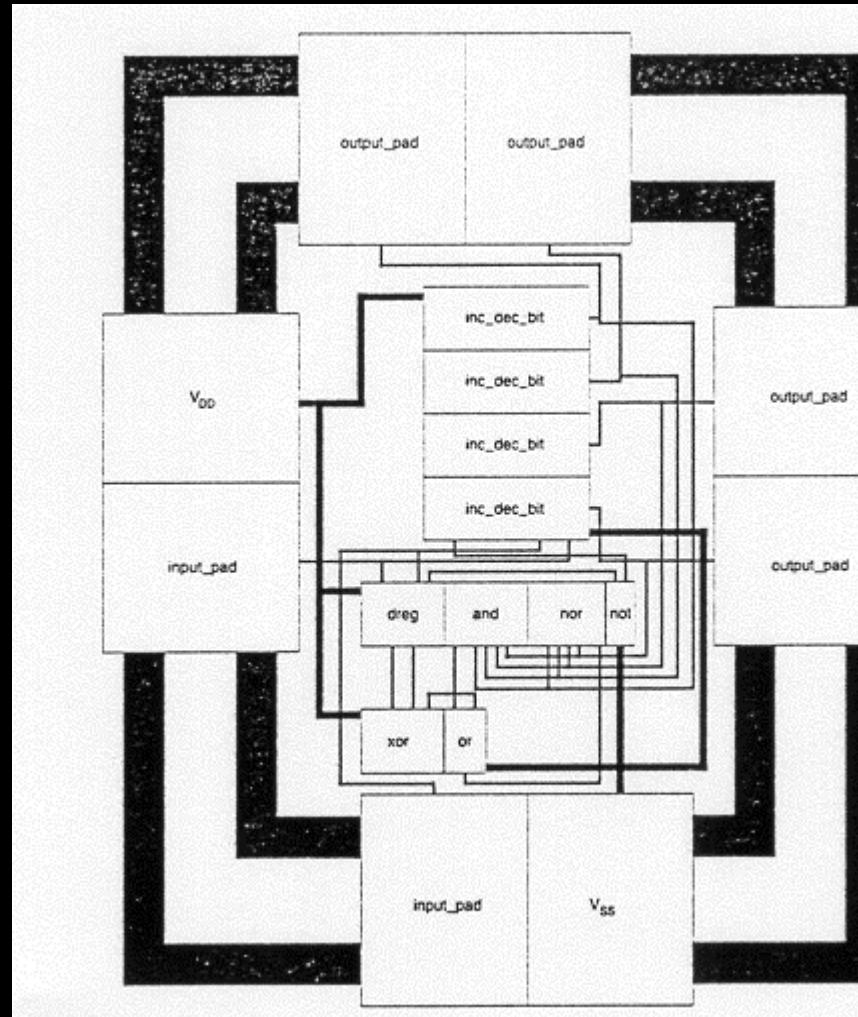

# Générateur de signaux triangulaires

écharchie structurelle et layout

correspondance physique pour

chaque module structurel

# Concepts de Régularité, Modularité, localité

- La Hiérarchie réduit la complexité du système

- D'autres considérations de conception sont nécessaires pour simplifier le processus

- La **Régularité** signifie que la décomposition hiérarchique doit aussi donner des blocs similaires autant que faire se peut

- Un bon exemple en est les structures en matrice de cellules identiques (multiplicateurs // par ex.)

- La Régularité peut exister à tous les niveaux d'abstraction

Au niveau transistor, des transistors de taille identique simplifie la conception

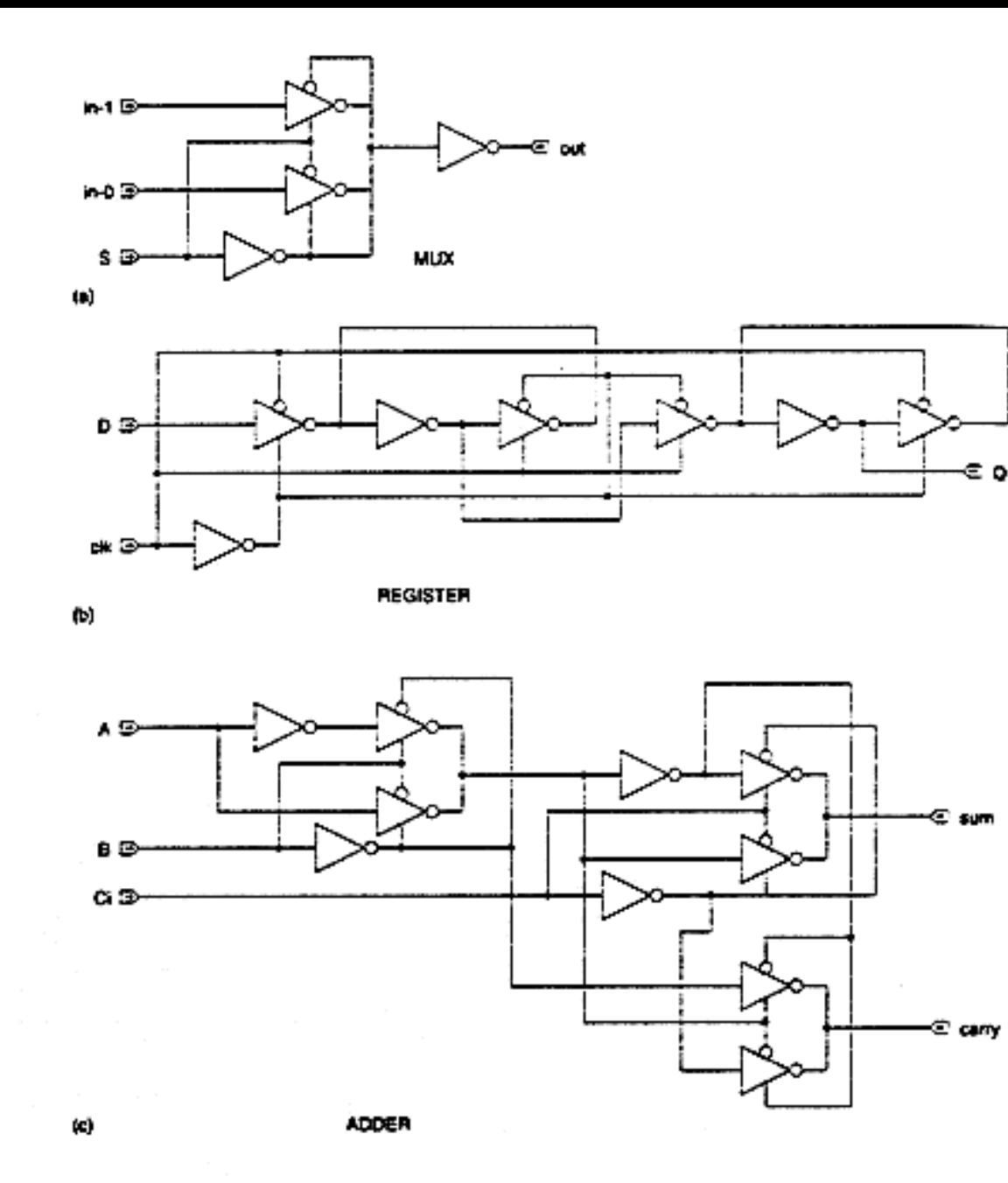

Au niveau logique, des structures de porte identiques peuvent être utilisées, la figure du transparent suivant montre une conception de type régulière au niveau circuit d 'un multiplexeur 2-1, d 'une Bascule D (front montant), et d 'un additionneur 1-bit

Tous ces circuits utilisent des inverseurs et de « buffers » tri-state seulement.

Si le concepteur a à sa disposition une librairie de blocs de base (caractérisés et bien définis), un certain nombre de fonctions peuvent être construites selon ce principe. On réduit de cette manière le nombre de modules à concevoir et à vérifier à tous les niveaux.

onception régulière

(inverseurs et tri-state)

Multiplexeur

Bascule D (edge-triggered)

Additionneur complet

Full-adder 1-bit)

- La Modularité signifie que les différents blocs fonctionnels constituant le système doivent avoir des interfaces et des fonctions bien définies

- La Modularité permet à chaque bloc ou module d'être conçu de manière relativement indépendante par rapport aux autres, du moment qu'il n'y ait pas d'ambiguïté à propos de la fonction et des signaux d'interface du bloc

- Tous les blocs doivent être combinés au final pour former le système complet

- La Modularité permet la parallélisation au niveau de la conception, ainsi que l'utilisation de modules génériques. Les fonctionnalités et les signaux d'interface permettent le « plug-and-play »

- La définition des interfaces (signaux fonctionnalités) permet de positionner la structure interne au niveau local, c'est le principe de **localité**

- Ce concept permet aussi d'assurer que les connexions entre les modules concernent des modules voisins de manière à éviter les connexions longue-distance. Ce dernier point est extrêmement important pour minimiser les délais d'interconnexions. Les opérations critiques en temps doivent être faites localement sans accéder à des modules ou signaux éloignés. Il est parfois nécessaire de dupliquer des fonctions logiques pour résoudre ce problème dans les architectures complexes

# Techniques de conception VLSI

- Plusieurs techniques existent (co-existent) pour l'implémentation des circuits intégrés. Chaque technique a ses avantages et ses inconvénients.

- Il appartient donc aux concepteurs de faire des choix de manière à assurer les fonctionnalités de manière optimale

- FPGA - « standard cells » - « Gate Array » et « Full custom » sont les différentes techniques accessibles au concepteur, nous nous intéresserons ici aux derniers

# Les « Gate-Array »

- En terme de prototypage rapide, les « Gate-array » (GA) viennent après les FPGA, en termes d'implantation le circuit FPGA est construit par programmation par l'utilisateur, alors que pour un « gate-array » l'implantation est faite au niveau des derniers masques de métallisation de la technologie (majoritairement des interconnexions).

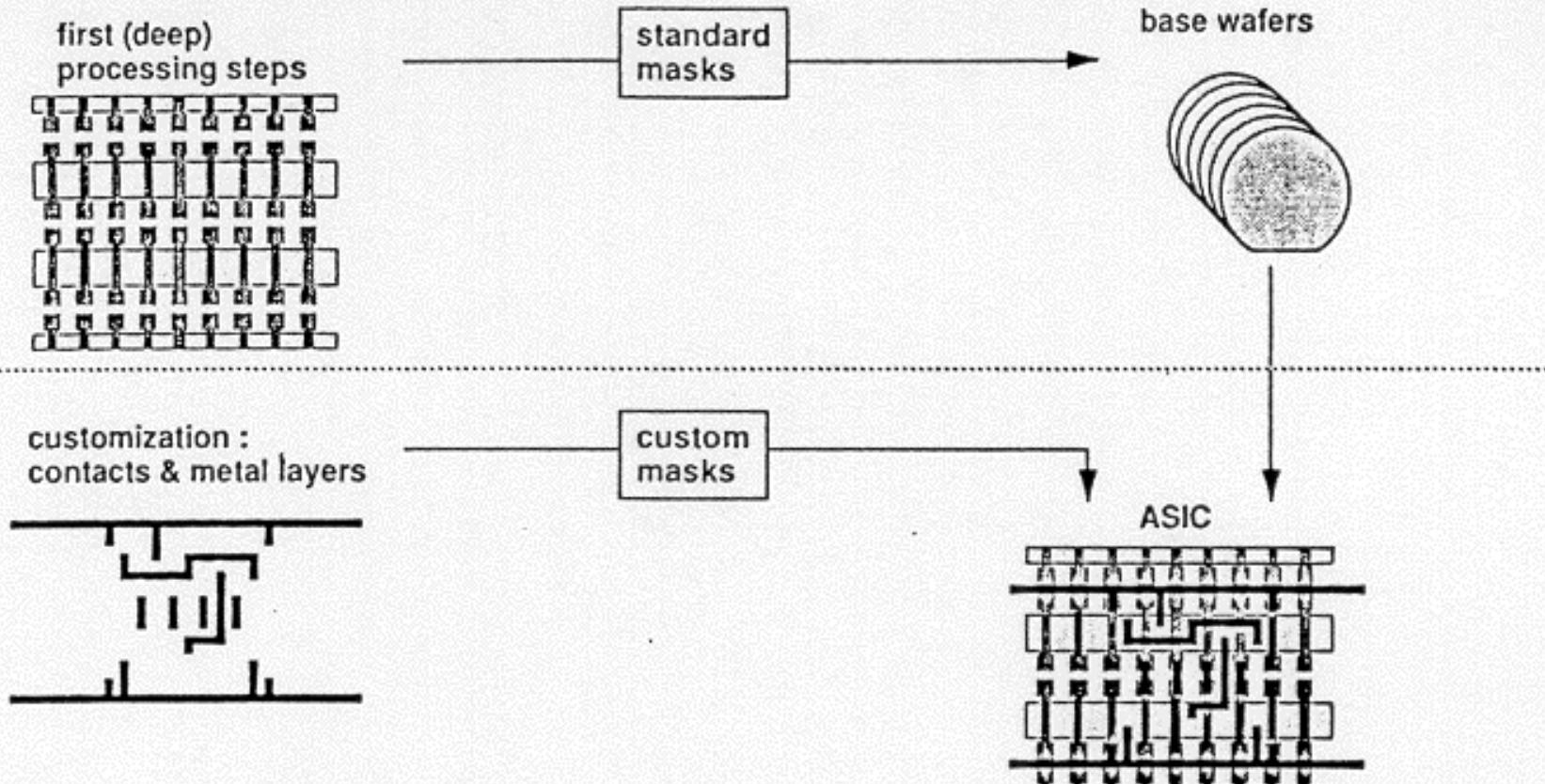

- L'implantation nécessite un process de fabrication en deux étapes :

- ◆ La première phase, basée sur des masques génériques (standard) résulte en une matrice de transistors pour chaque circuit de type GA

- ◆ Ces circuits sont disponibles pour personnalisation ultérieure, par la définition des interconnexions métalliques entre les transistors de la matrice (ou réseau). Comme la phase de métallisation est faite à la fin du cycle de fabrication, le temps de retour peut être assez court (quelques jours à quelques semaines)

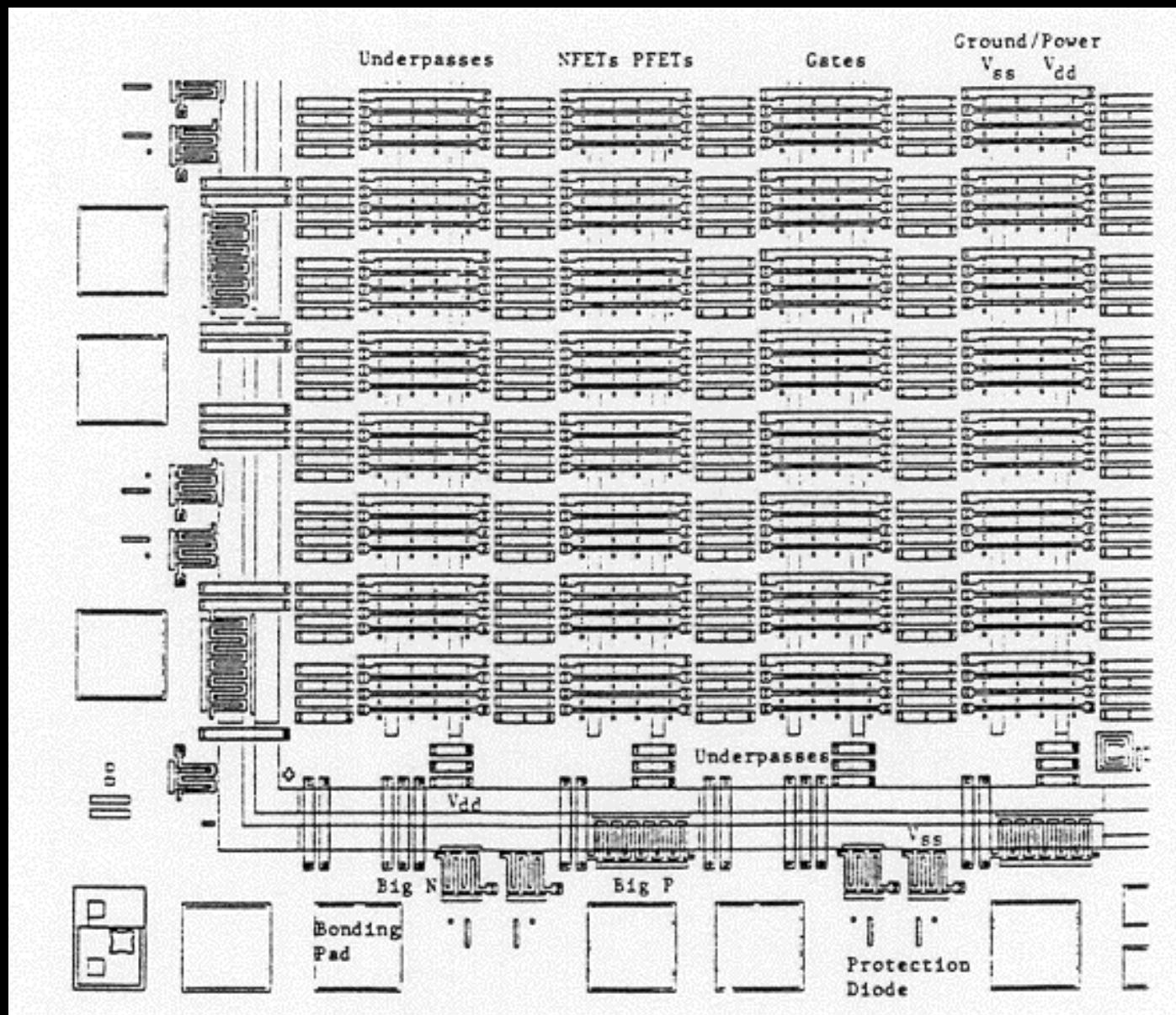

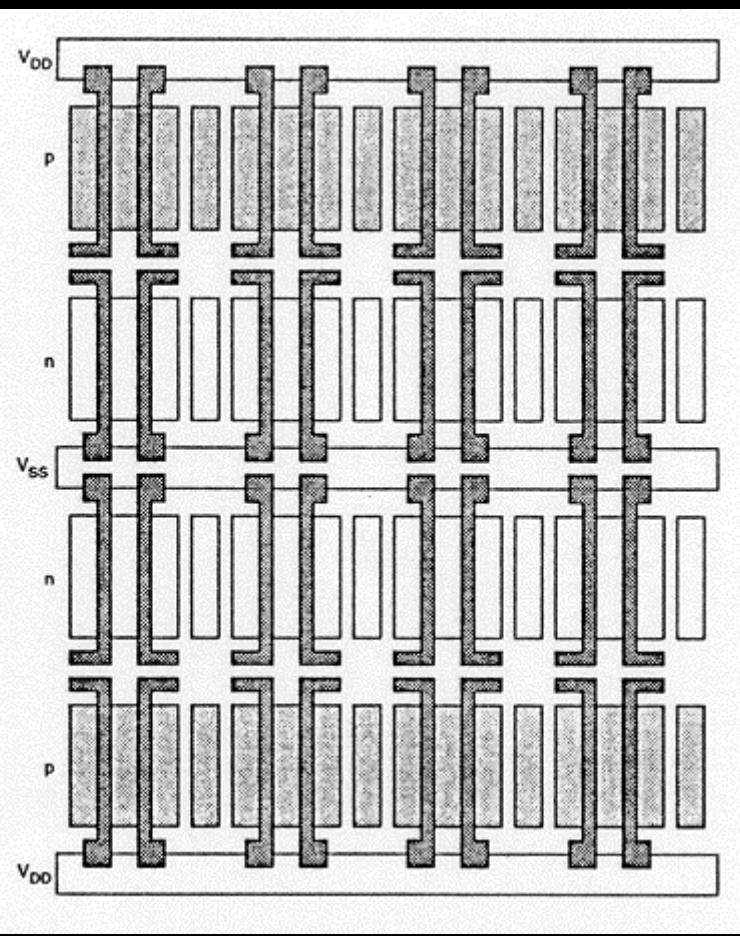

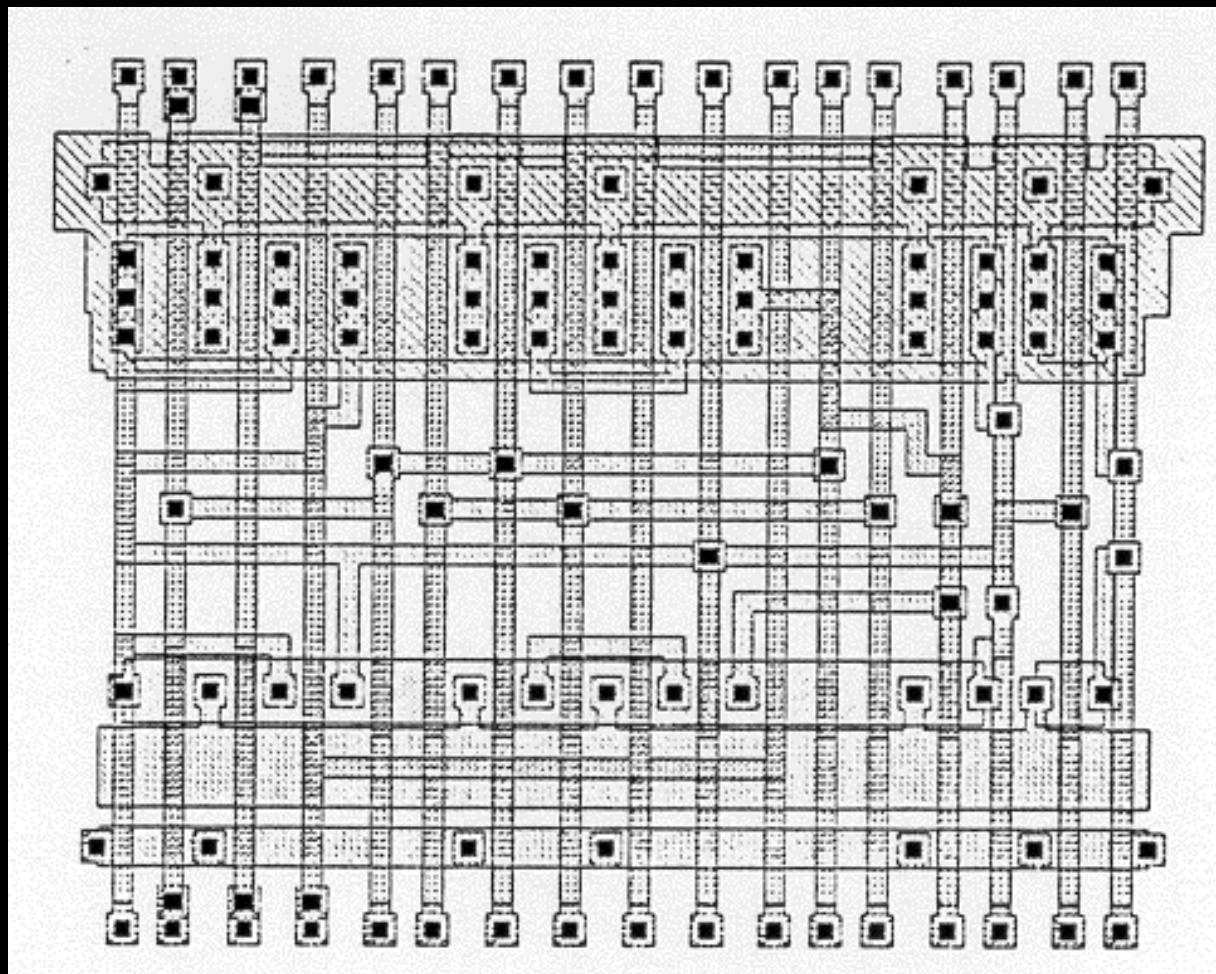

- Les figures suivantes montrent le procédé et un détail de circuit avec les pattes de connexion et les diodes de protection, des transistors NMOS et PMOS pour les « drivers » de sortie, les matrices de transistor (PMOS et NMOS), des lignes d'interconnexions, les lignes d'alimentation (VDD-VSS) et les contacts

## two-step manufacture :

Etapes de fabrication pour un procédé de type « Gate-Array »

Partie inférieure d 'un circuit de type « Gate-Array »

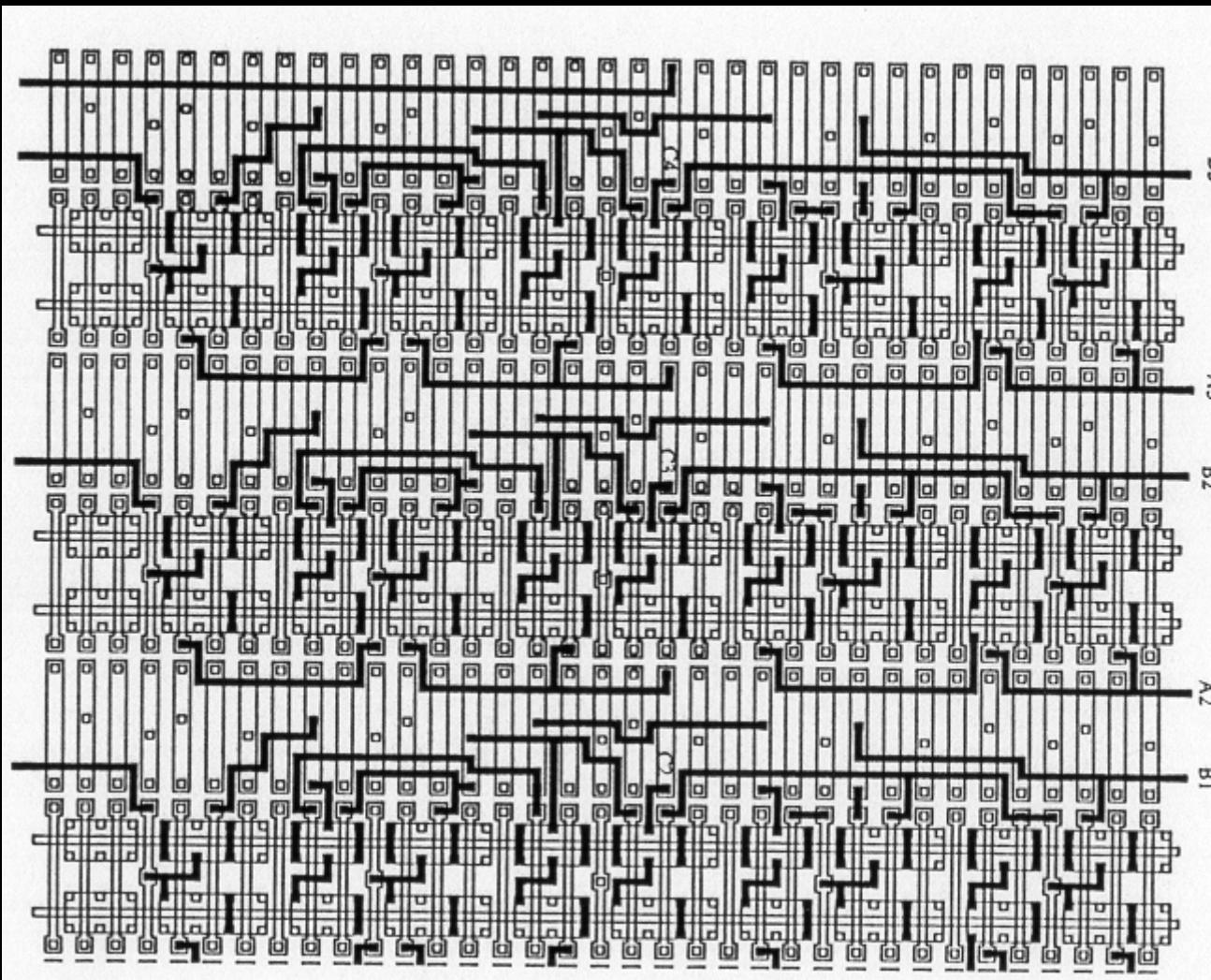

- La figure suivante montre un agrandissement d 'une partie du réseau avec les lignes de métallisation représentées pour réaliser une fonction logique complexe.

- Les « Gate-Array » typiques ont des parties particulières appelées des canaux (« channels ») pour le routage inter-cellules (voir les 2 figures précédentes) entre les lignes et les collones des transistors MOS. La disponibilité de ces canaux de routage simplifie les interconnexions, même si l'on utilise une seule couche de métallisation.

- Les interconnexions permettant de réaliser des fonctions logiques de base peuvent faire partie d'une bibliothèque (library) qui sera utilisée pour personnaliser le réseau de transistors en accord avec la « netlist ».

- La majorité des « gate-array » contiennent uniquement des réseau de transistors séparés par des canaux de routage.

- Cependant quelques plate-formes offrent de mémoires dédiés (RAM) pour permettre une plus grande densité d'intégration quand des fonctions mémoire sont nécessaires

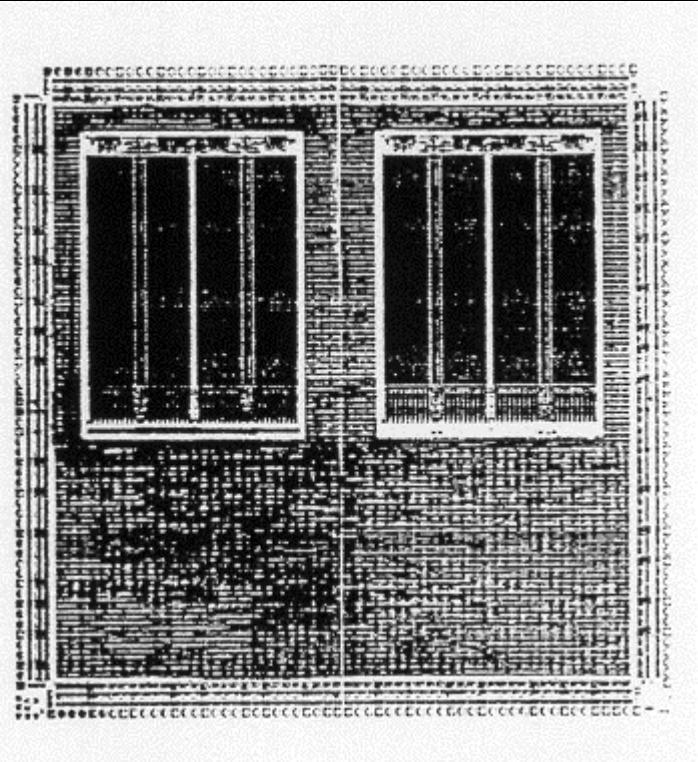

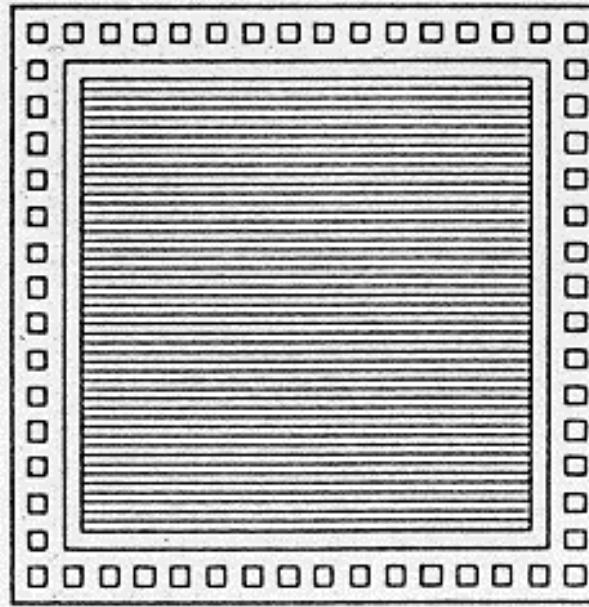

e-array conventionnel et « gate-array » avec deux bancs mémoires

L 'utilisation de plusieurs couches d 'interconnexions permet de faire du routage au-dessus des cellules; ainsi les canaux de routage adjacents peuvent disparaître donnant des circuits de type « mer-de-portes » (« sea-of-gates » SOG) pour lesquels la surface est complètement occupée par les transistors NMOS et PMOS. Des transistors voisins peuvent de la même manière que précédemment être personnalisés pour former des fonctions de base, cependant pour le routage entre les cellules certains des transistors doivent être sacrifiés. Cette approche permet une plus grande flexibilité pour les interconnexions et généralement une plus grande densité.

- La figure ci-contre montre la plate-forme de base d 'un SOI. En général le taux d 'utilisation d 'un GA correspond au rapport de la surface utilisée sur la surface totale du circuit.

- Il est généralement supérieur à celui obtenu pour les FPGA, même pour la vitesse puisque la personnalisation est

meilleure avec les techniques de routage de type métallisation utilisées.

Les techniques actuelles permettent d 'implémenter de certaines de milliers de fonctions logiques

**routing problem is simpler**

**OK with only one metal**

**flexibility in channel definition (position & width)**

**over-the-cell routing**

**higher packing density**

**RAM-compatible**

**supports variable-height cells & macrocells**

**now universally used**

comparatif des « gate-array » avec canaux de routage

des « Sea-of-gates »

# Les « Standard-cells »

- Les techniques de type « standard-cells » requièrent le développement d 'un jeu complet de masques de fabrication, on les appelle aussi « polycell ». Dans cette technologie toutes les cellules communément utilisées sont développées, caractérisées et stockées dans une bibliothèque de cellules.

- Une bibliothèque classique contient quelques centaines de cellules (inverseurs-portes amplificateurs-Bascules-etc..). Chaque porte peut avoir des implantations multiples pour par exemple fournir des capacités de pilotage différentes..

- Par exemple, l'inverseur peut avoir des transistors de type standard ou double taille ou quadruple taille pour permettre au concepteur de choisir la bonne solution en terme de vitesse et surface pour le circuit.

- La caractérisation de chaque cellule est faite pour différentes catégories :

- ◆ délai vs. Capacité de charge

- ◆ modèle de simulation circuit

- ◆ modèle de simulation timing

- ◆ modèle de simulation de fautes

- ◆ données de cellule pour le placement et le routage

- ◆ données de masquage

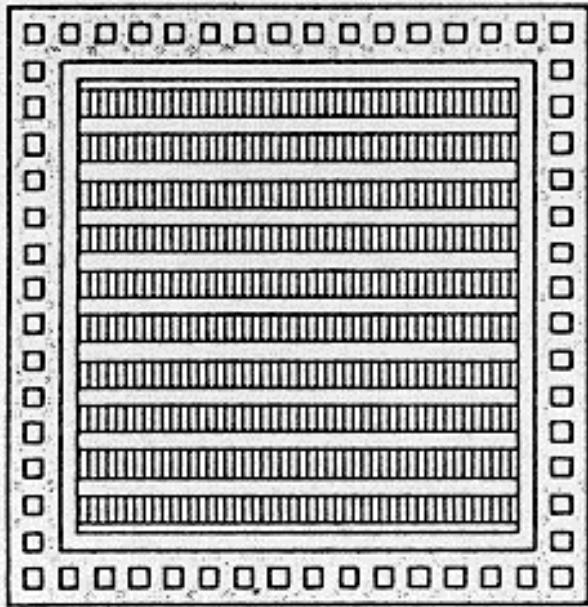

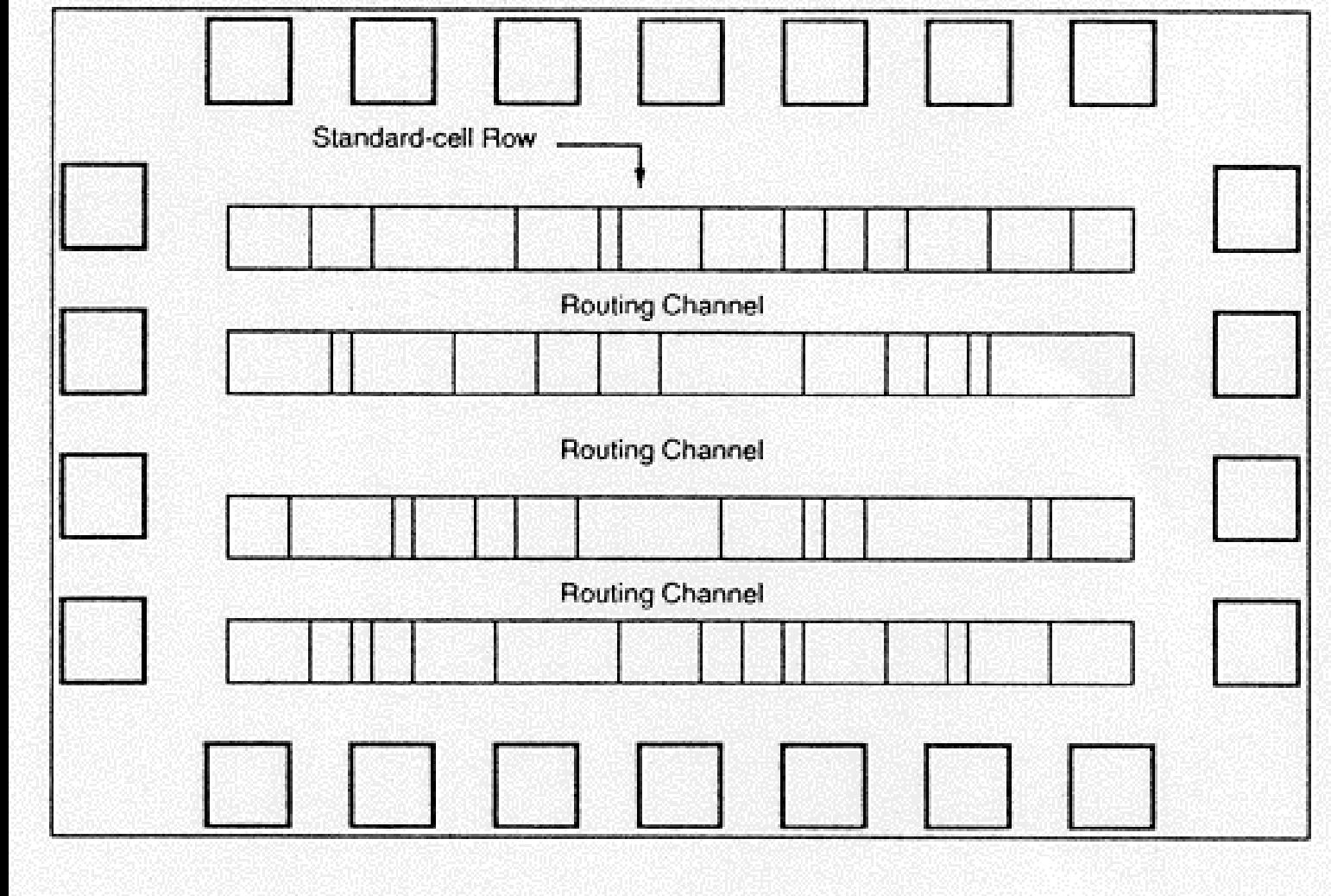

- Pour permettre le placement automatique de cellules et le routage des interconnexions entre les cellules, chaque « layout » de cellule correspond à une hauteur fixe de manière à ce qu'elles puissent être mises en forme par rangées. Les lignes d'alimentation sont typiquement parallèles au-dessus et au-dessous des cellules de manière à ce qu'elles partagent un bus commun d'alimentation.

- Les pattes d'entrée-sortie sont placées sur les frontières supérieures et inférieures de la cellule.

- La figure suivante donne un aperçu typique d'un « layout » de standard-cell. On peut noter que les NMOS sont proches de la masse et les PMOS proche de l'alimentation.

- Exemple de layout pour un standard-cell

- La figure suivante montre le « floorplan » (plan au sol ou plan d'implantation) pour un circuit standard-cell. A l'intérieur de l'emplacement réservé pour les cellules I/O, la surface du circuit est occupée par des rangées et des colonnes de cellules standard.

- Entre les rangées figurent des canaux dédiés au routage inter-cellules. Comme dans les « sea-of-gates », avec routage par-dessus les cellules, la surface des canaux peut être réduite voire supprimée sous réserve que les rangées de cellules offrent suffisamment d'espace de routage. La conception des cellules permet les connexions naturelles pour les lignes d'alimentation de chaque rangée.

Vue synoptique du « floorplan » d'un circuit « standard-cells »

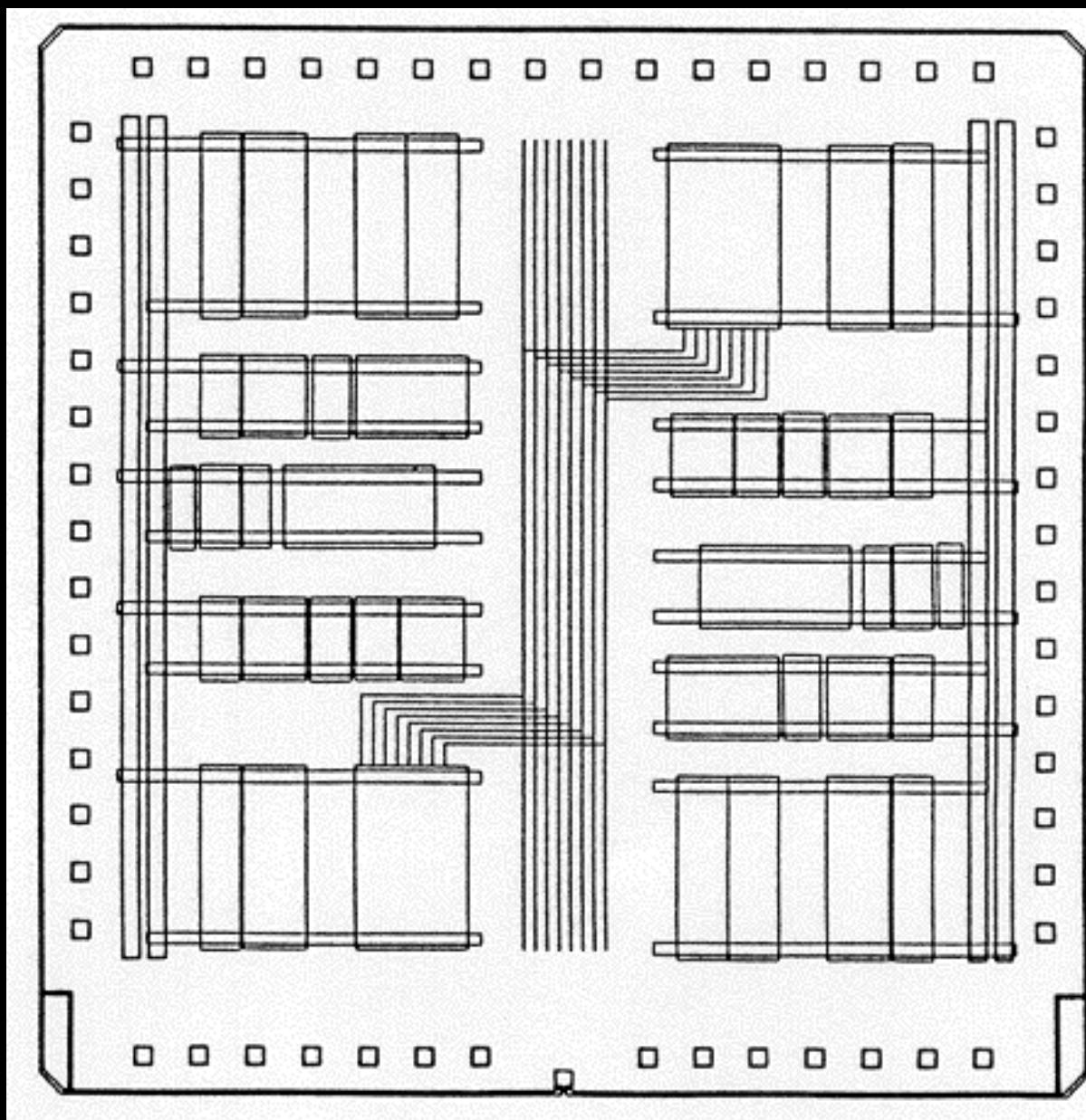

- Si plusieurs cellules doivent partager les mêmes signaux d'entrée-sortie, une structure de signaux du type bus peut être incorporée au niveau d'« layout ». La figure suivante montre un tel exemple (vue symbolique) où un bus a été inséré entre les rangées des standard-cells. On peut noter que dans ce cas le circuit comporte 2 blocs, et que le routage alim/masse doit être assuré des deux côtés de la surface du layout.

- Les circuits « Standard-cell » peuvent contenir plusieurs de ces « macro-blocs », correspondant par exemple à une ALU, de la logique de contrôle, etc..

« floorplan » avec 2 blocs et un bus signal commun

# Conception « Full-Custom »

Bien que les « standard-cells » soient souvent assimilés à du « Full-custom » ce n'est pas strictement exact puisque les cellules sont pré-conçues pour un usage général et qu'elles peuvent être utilisées dans plusieurs circuits. Dans une conception « Full-custom », la totalité du masque est faite sans l'utilisation de librairies. Conséquent le coût de développement est très élevé. Aussi le concept de réutilisation devient de plus en plus populaire. D'un point de vue rigoureux, cela peut correspondre à une cellule mémoire (statique ou dynamique) avec ensuite duplication car il n'y a pas d'autre alternative pour atteindre une haute densité.

Pour les circuits logiques complexes, on peut arriver un bon compromis en utilisant une combinaison de différents types de conception pour le même circuit « standard-cells » - blocs de données - PLAs.

Pour un vrai « Full-custom », pour lequel la géométrie, l'orientation, le placement de chaque transistor est faite individuellement par le concepteur, la productivité est basse, typiquement de l'ordre de 10 à 20 transistors par jour et par concepteur.

Pour les circuits numériques VLSI CMOS, le « full-custom » est rarement utilisé à cause de son coût élevé. Parmi les exceptions, on peut signaler les mémoires, les microprocesseurs haute-performance (super-scalaires-super pipelines) et les matrices d'EPGA.

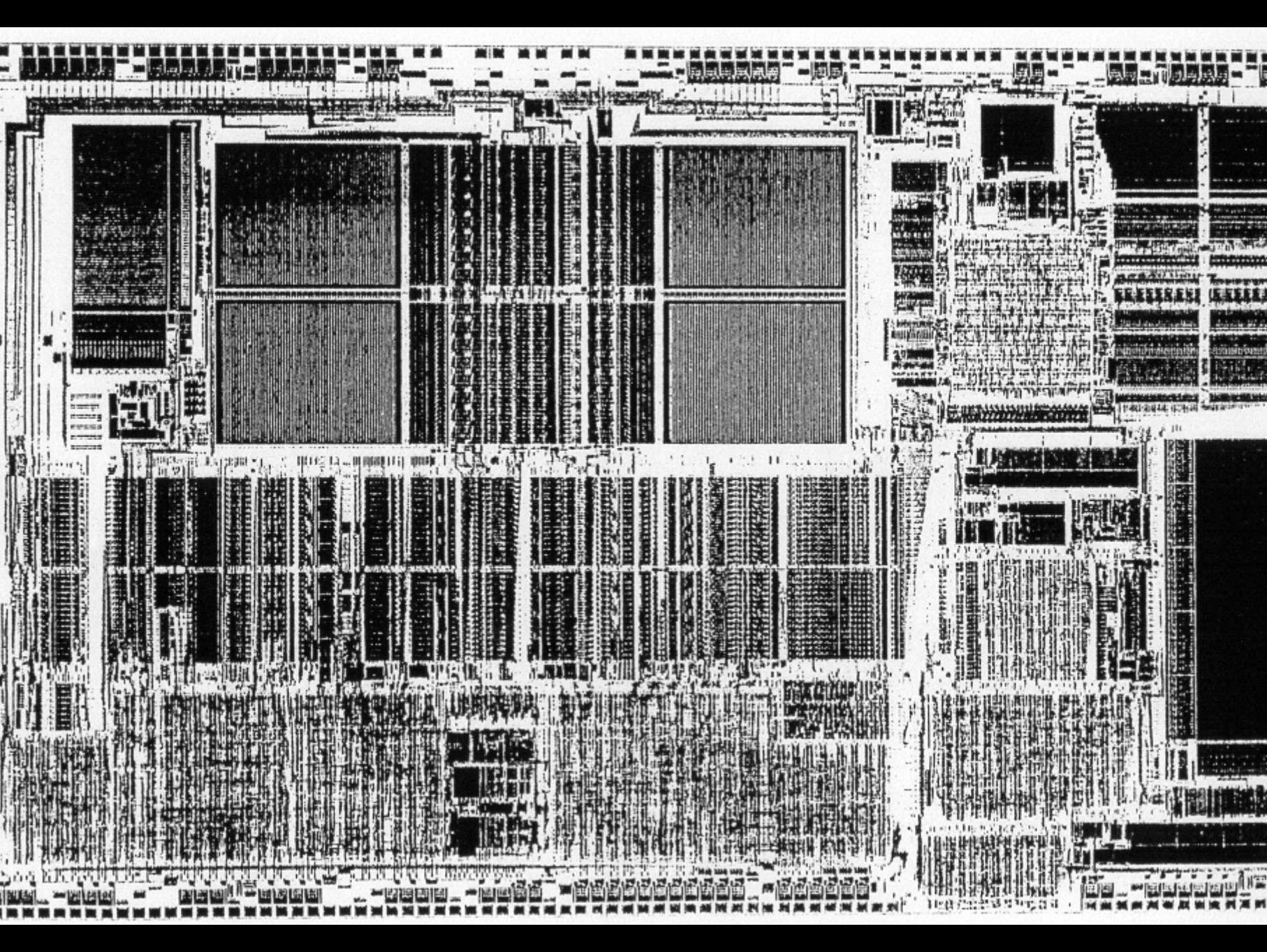

- La figure suivante montre le microprocesseur 486 d 'Intel, qui, malgré son grand âge, est un bon exemple de conception hybride intégrant du « full custom ».

- On peut identifier 4 types de blocs :

- ◆ les bancs mémoires (cache en RAM)

- ◆ les unités « data-path » (cellules de calcul par bit)

- ◆ les circuits de contrôle (standard cells)

- ◆ les blocs PLA

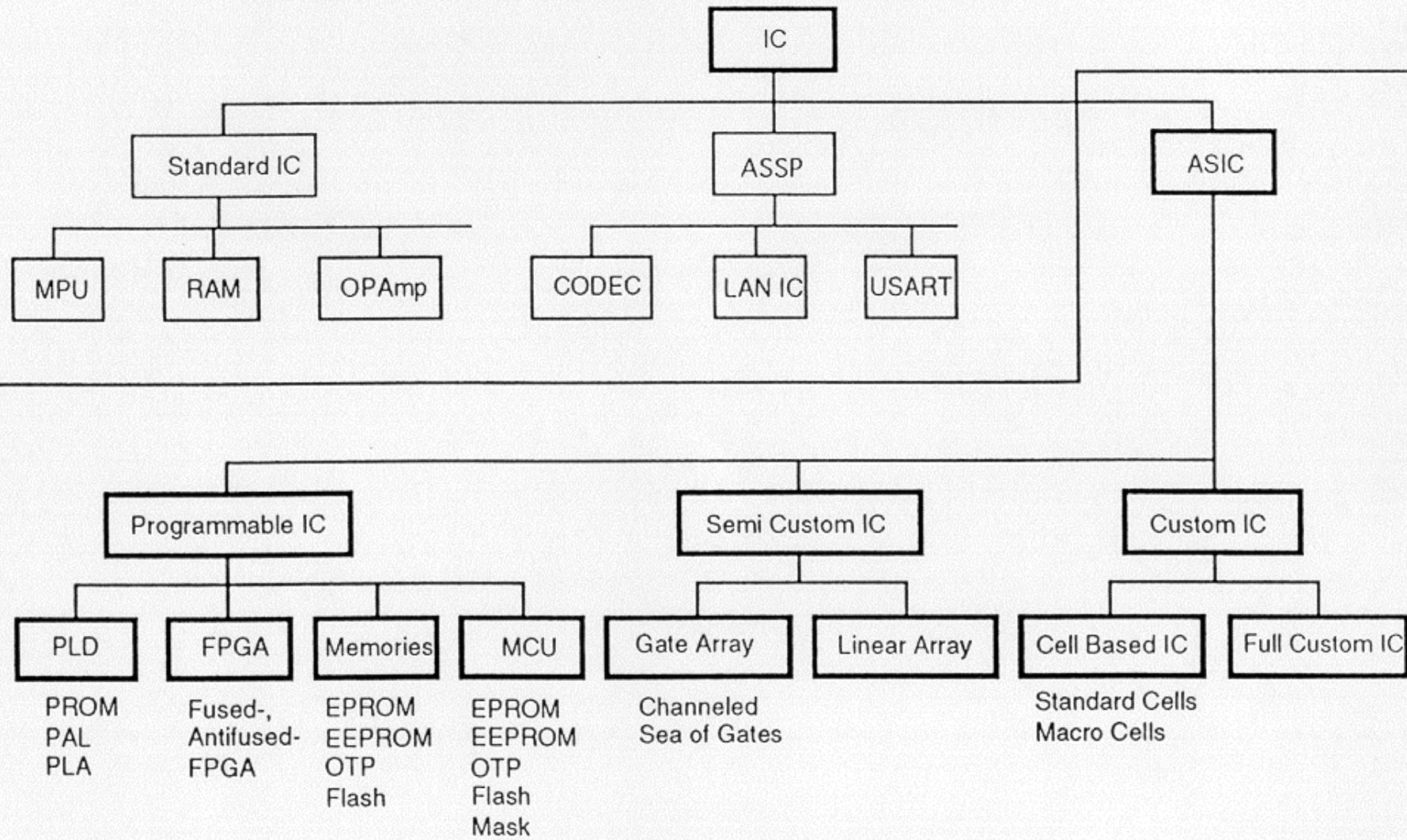

# Arbre « génalogique des CI »